您好,

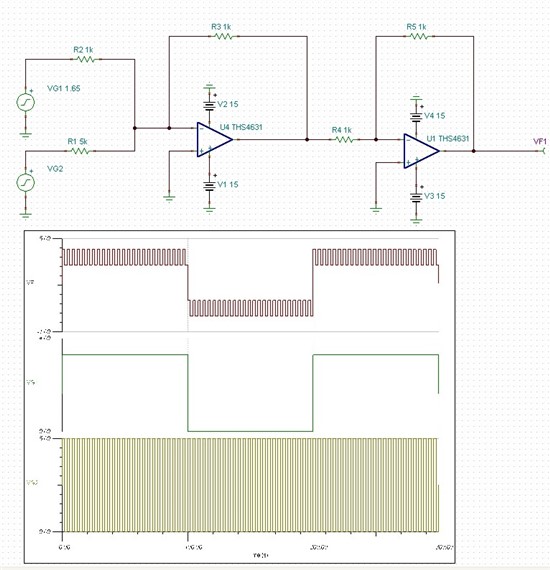

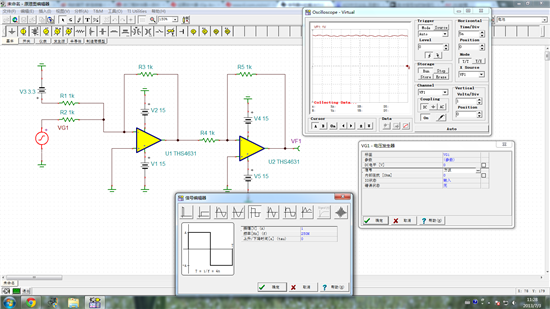

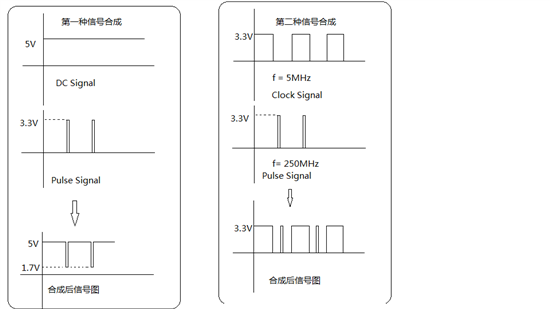

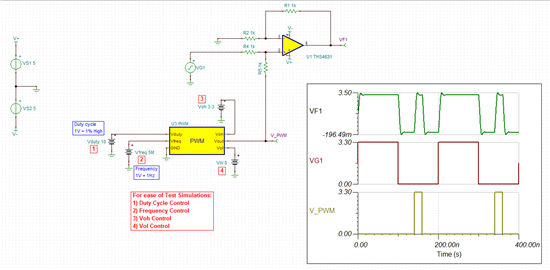

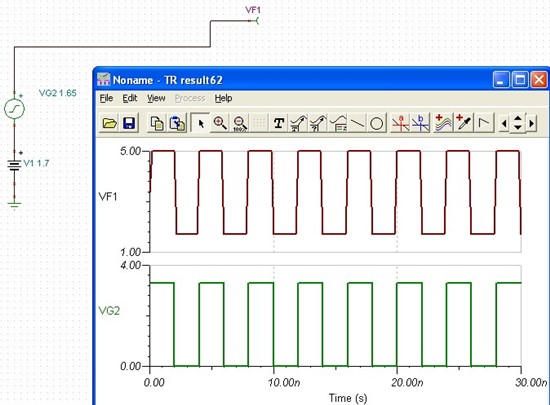

我使用FPGA产生一个5MHz的时钟信号,0V-3.3V。为了测试产品的稳定性,需要在这个时钟信号的低电平位置叠加一个脉冲信号,此脉冲信号也是由FPGA产生,频率约为250Mhz。

我的问题是:

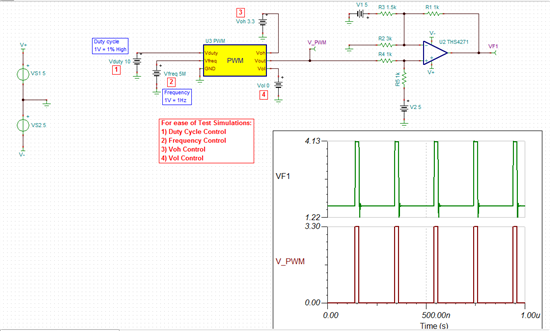

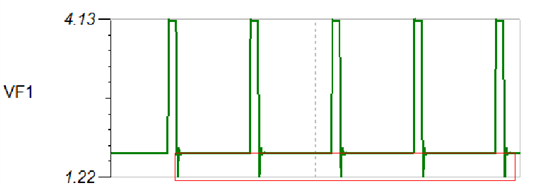

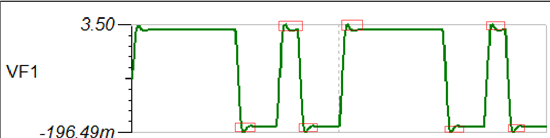

①:怎样控制脉冲信号的幅值,使其可以在0V到5V内可控?如需选用放大器,请问我需要的放大器的带宽满足什么条件?

②:怎样把脉冲信号叠加到时钟信号上?

③:怎样把反向脉冲信号(一直是3.3V,当有触发的时候为0V,250MHz)叠加到5V的直流电源上?

④:我把5M的时钟信号分别经过TLE2072(做跟随器)和THS3062(跟随器)这两个运放组成的跟随器,但是输出的时钟信号完全变形,类似于三角波。请问这是为什么?