Other Parts Discussed in Thread: OPA690

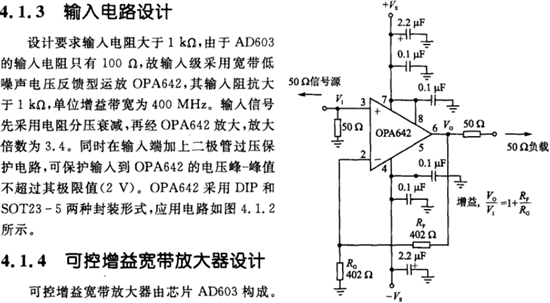

我要设计的是一个宽带放大器(电赛2003B题),题目中要求输入阻抗≥1KΩ,那么这里所说的1K是怎样一个概念,就是说是指哪里的阻抗,怎样测得的?我理解为用万用表直接接到电路的信号输入端所得到的阻抗值,这样理解对吗??如果是这样的,请看图片,图片是前置阻抗匹配电路,这样按照我所理解的测试方法测得的阻抗必然≤50Ω,这应该如何解释呢?图中输入端的50Ω电阻是为了和信号源的50Ω内阻相匹配的。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

虽然我也不是很明白,不过可以看看这篇文章,或许有点帮助。http://www.dz863.com/all-technology/Electronics-Glossary/Smith-circuits.htm

"题目中要求输入阻抗≥1KΩ",是单纯指的运放的输入阻抗,此时不应该将并联的50欧姆考虑在内。你并联50欧姆电阻是为了更好地实现信号的传输,与前面信号源的阻抗相匹配。换个角度思考一下,如果你运放的输入阻抗≥1KΩ,与50欧姆阻抗并联得到的阻抗值很接近50欧姆,然而若输入阻抗值不是很大,这时再与50欧姆阻抗并联就不是很接近50欧姆,也就会影响到信号传输的质量。

运放级联时,前级输出阻抗很小,后级尽量用同相放大器,这样后级输入阻抗非常大,这时两级间不需要阻抗匹配了吧,

我觉得加50欧阻抗匹配,只是用在测试时与函数发生器和示波器匹配,不知道对不对,希望大家指点下。

还有就是示波器表笔负载和示波器负载都上兆欧,为什么要串联50欧电阻啊

一般相同芯片级联之间不需要匹配,与不同芯片连接时要做匹配