Other Parts Discussed in Thread: DEM-OPA-SO-1A, LMH6702

上一小节从理论上分析了CFB运放负向输入端的分布电容的影响。大家可能觉得还是很空洞。下面将从实验结果来验证上面的理论。(我总是喜欢先从理论的角度分析一个问题,然后再用实验来验证。有了实验结果,会让理论更形象,也更让人记忆深刻)。

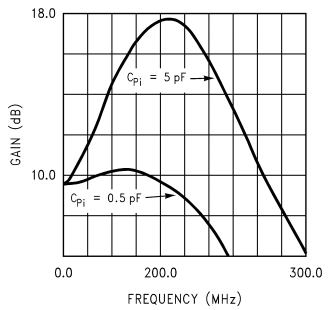

下面是工程师Michael Steffes用老的CFB运放做的实验结果。它在上一小节的输入电容的位置,分别用0.5pF和5pF的电容做的实验。当负相输入电容为5pF时。带内就非常不平坦了。这个实验被发表在上世纪90年代初的论文上。

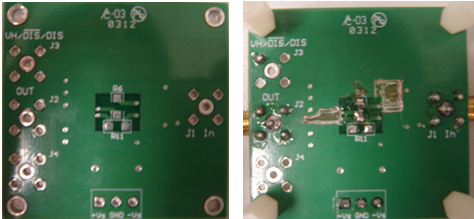

同大家一样,我也觉得论文中的曲线很空洞。对分布电容到底有没有这么大的影响,还是持怀疑态度。我自己用运放的通用评估板DEM-OPA-SO-1A做了测试。如下图

https://estore.ti.com/DEM-OPA-SO-1A-DEM-OPA-SO-1A-P833.aspx

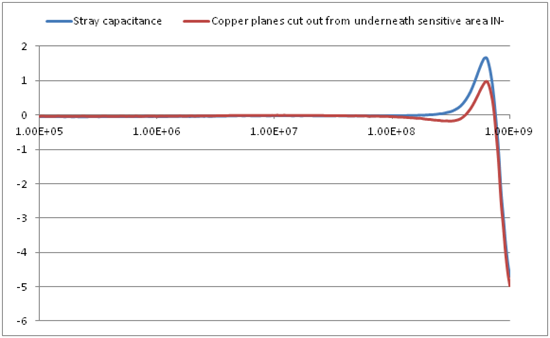

这块评估板的输入走线下面的地,没有开窗挖掉,因此它与地层形成分布电容。 我先测试LMH6702在这块评估板上的频响曲线。然后再把负向输入引脚走线的地层铜皮挖掉。再次测试频响。结果不出所料,高频过冲得到了很大的减弱。如下图。看到了吧,仅仅是负向输入引脚及走线与地平面形成的毛毛雨量级的电容,就成带来这样的影响。因此得出第一个得重要结论,在CFB放大电路PCB layout时,为了降低输入分布电容的影响。要把负向输入引脚及走线下方的地层开窗挖掉。

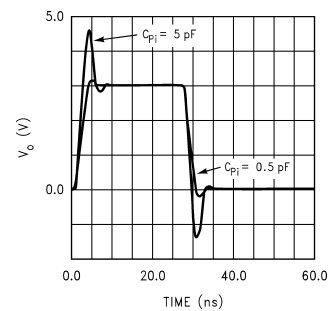

最后再聊一点,如果CFB运放负向输入引脚的分布电容非常非常小,它一般只会使得高频增益变大。如果这个分布电容变大了这么一点点,它可能会引起相位裕度明显降低,甚至震荡。怎么评估呢,看放大电路对阶越信号的响应,如下图。不多说,一目了然。