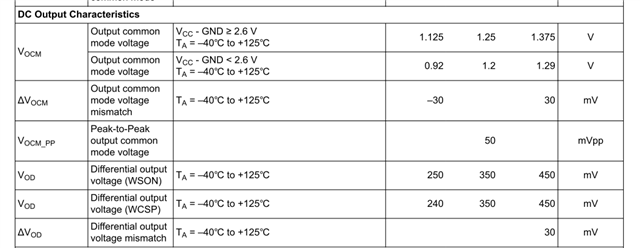

Part Number: TLV3801

Other Parts Discussed in Thread: LMK00301, LMK04832, SN65LVDS100

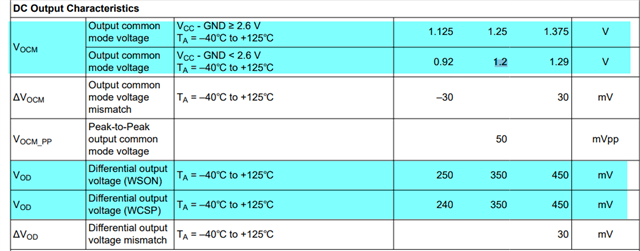

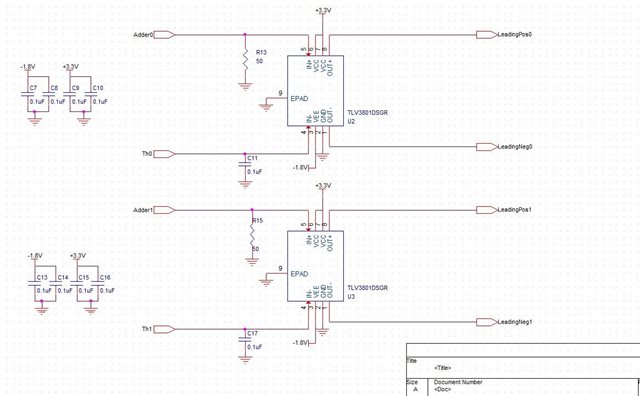

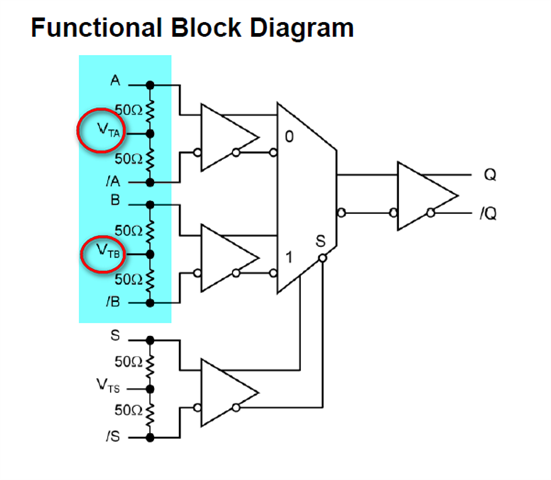

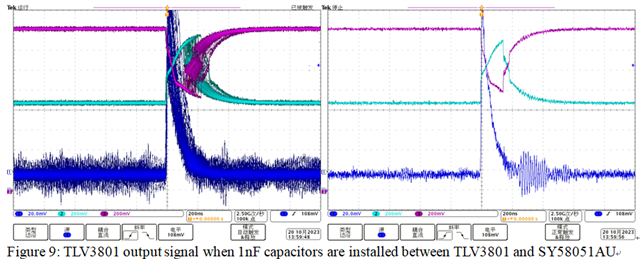

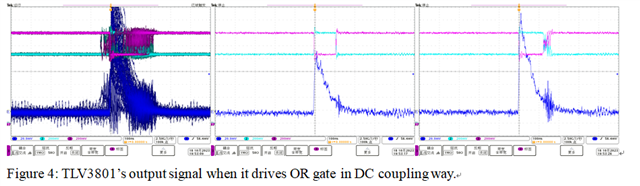

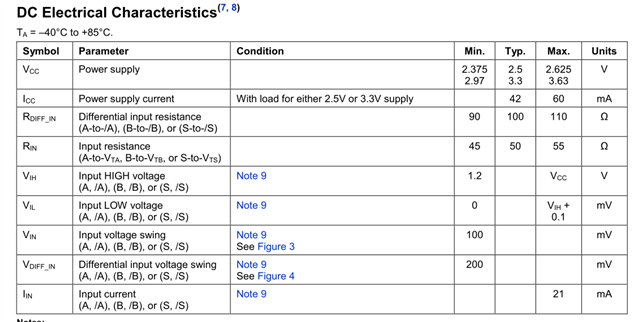

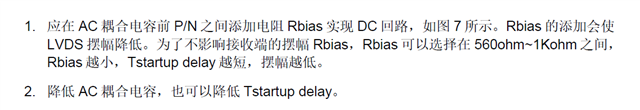

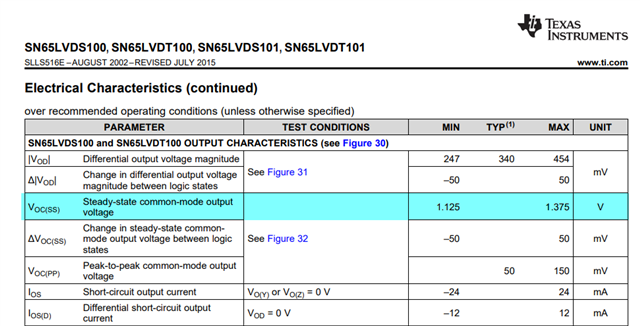

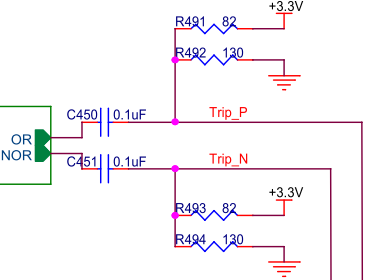

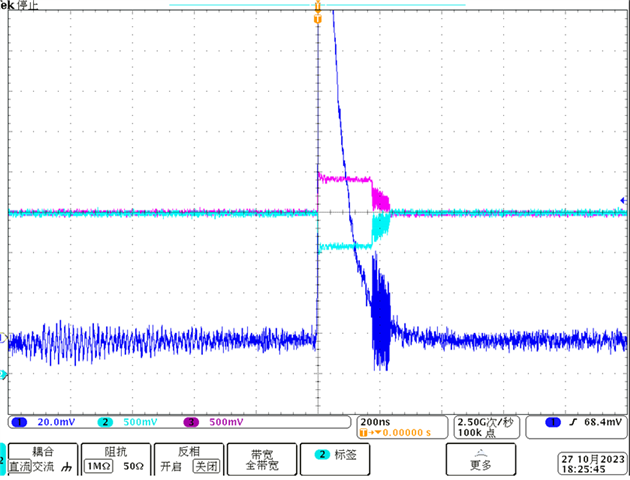

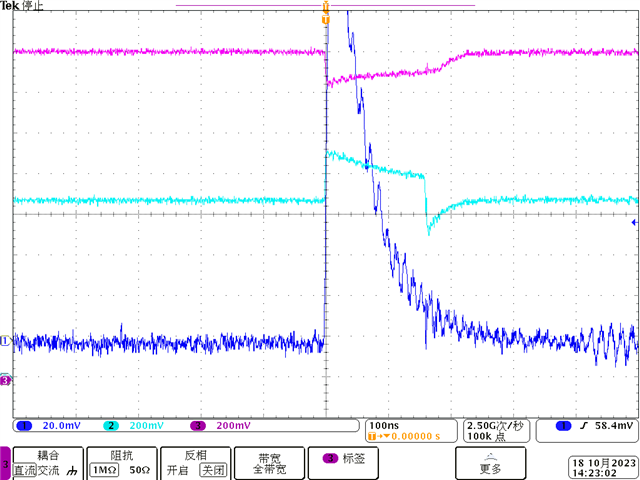

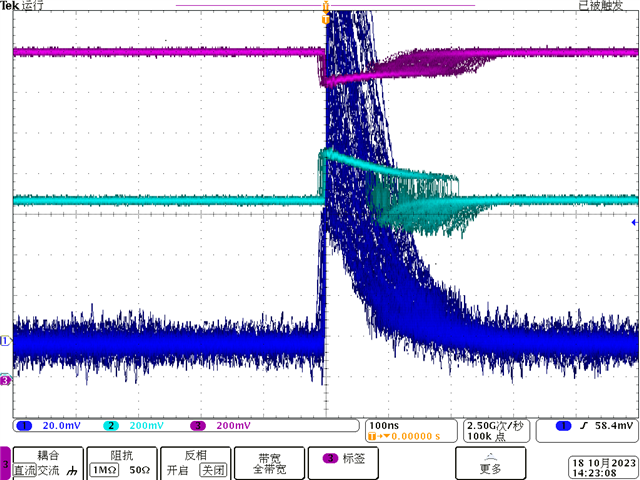

我们使用TLV3801作为比较器,输入信号为指数脉冲,比较基准来自DAC,设置为20mV。比较器的输出波形异常,而且似乎Q+和Q-的直流电平相距过大,或者是输出摆幅过小?如图所示

示波器通道1测量的是输入信号,通道2,3分别测量TLV3801输出的Q+和Q-。正常脉冲Q+与Q-幅度(摆幅)应该完全交叉,对吧?

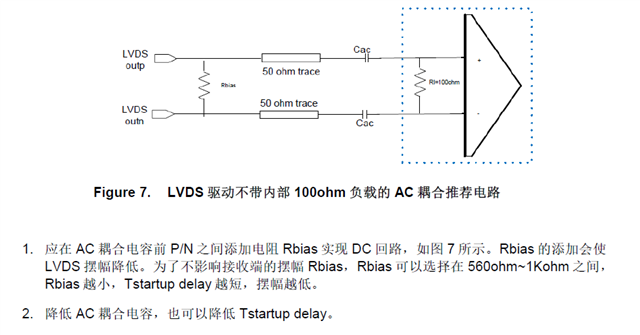

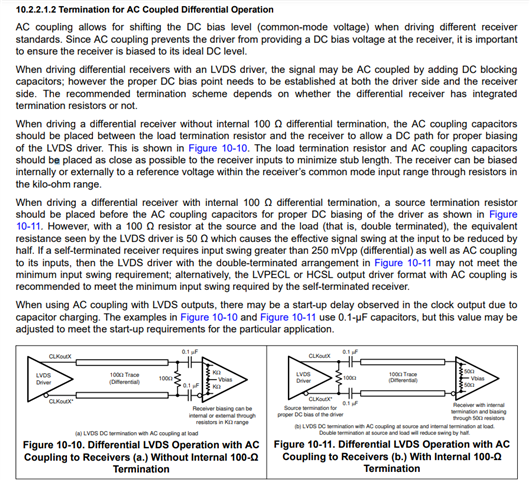

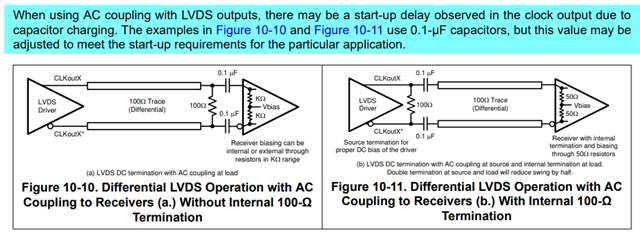

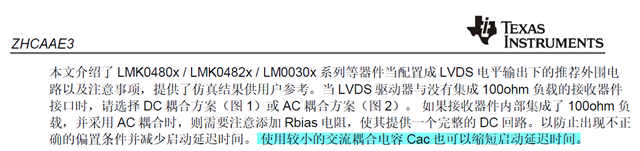

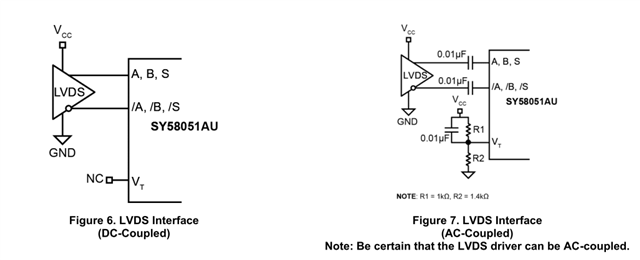

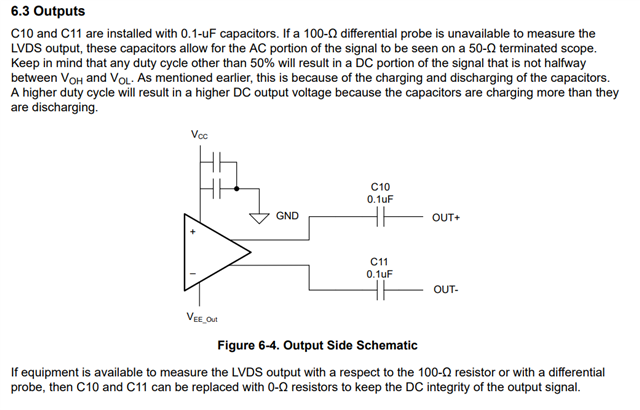

BTW,TLV3801的输出是否支持AC耦合?