Other Parts Discussed in Thread: LMK00301, LMK04832, SN65LVDS100

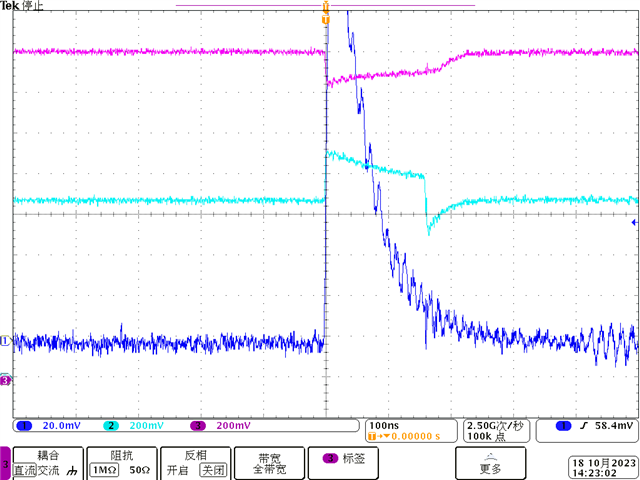

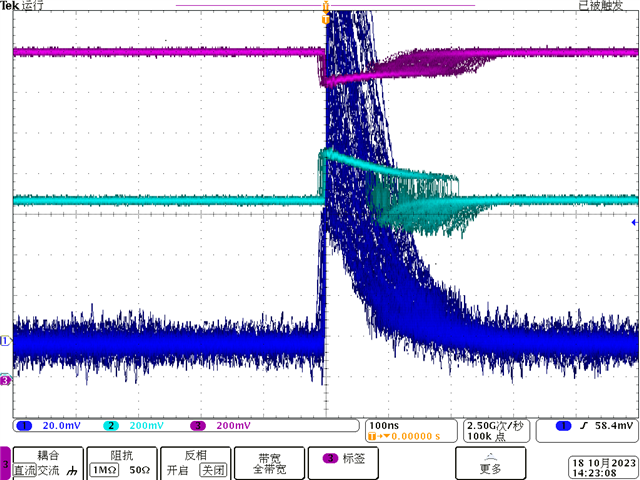

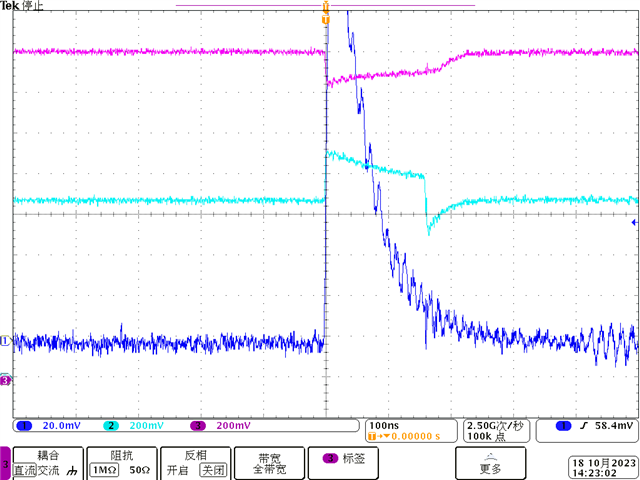

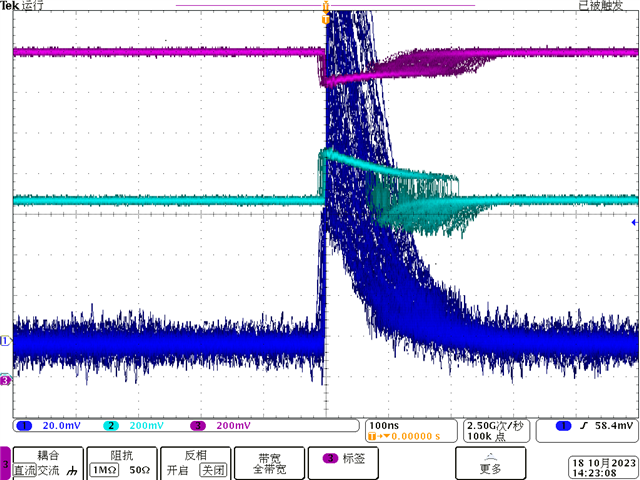

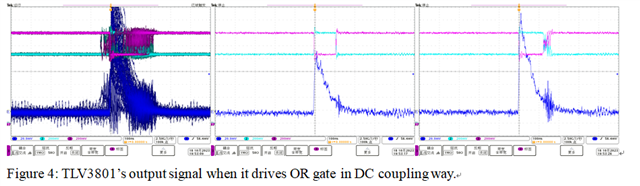

我们使用TLV3801作为比较器,输入信号为指数脉冲,比较基准来自DAC,设置为20mV。比较器的输出波形异常,而且似乎Q+和Q-的直流电平相距过大,或者是输出摆幅过小?如图所示

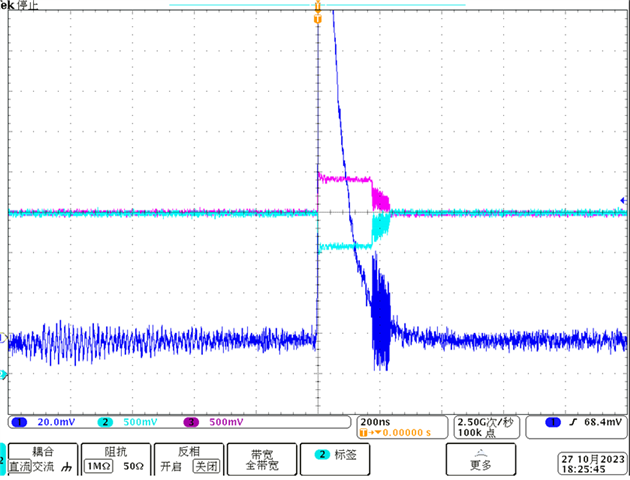

示波器通道1测量的是输入信号,通道2,3分别测量TLV3801输出的Q+和Q-。正常脉冲Q+与Q-幅度(摆幅)应该完全交叉,对吧?

BTW,TLV3801的输出是否支持AC耦合?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

我们使用TLV3801作为比较器,输入信号为指数脉冲,比较基准来自DAC,设置为20mV。比较器的输出波形异常,而且似乎Q+和Q-的直流电平相距过大,或者是输出摆幅过小?如图所示

示波器通道1测量的是输入信号,通道2,3分别测量TLV3801输出的Q+和Q-。正常脉冲Q+与Q-幅度(摆幅)应该完全交叉,对吧?

BTW,TLV3801的输出是否支持AC耦合?

您好,

正常脉冲Q+与Q-幅度(摆幅)应该完全交叉,对吧?

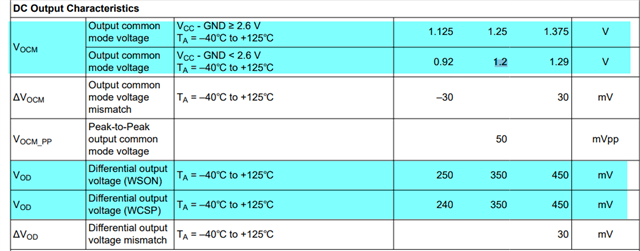

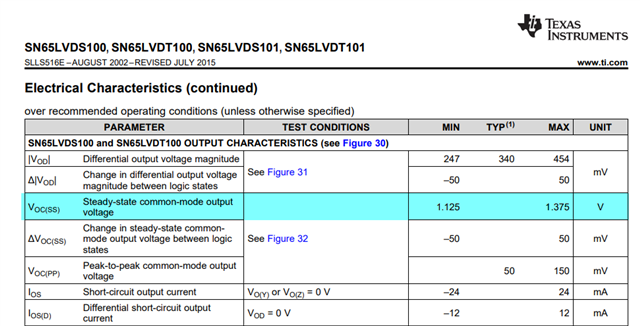

是的,它们有输出共模电压如下截图所示,输出摆幅也不对。您可以附上测试电路吗?测试时负载端是怎样连接的?

BTW,TLV3801的输出是否支持AC耦合?

您是说接收端是AC耦合输入吗?这应该是可以的,但应该有输入端的偏置电路以满足接收端的共模电压。

Amy, 你好,

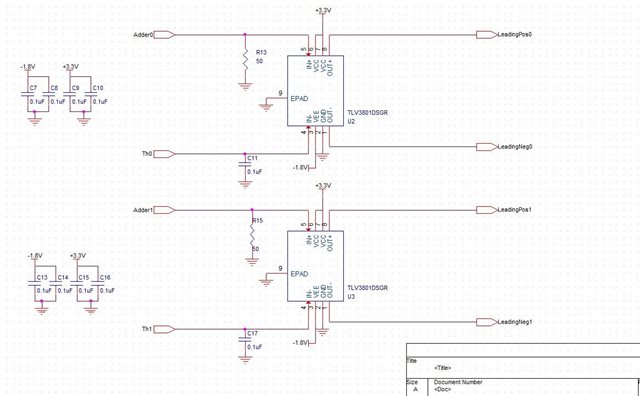

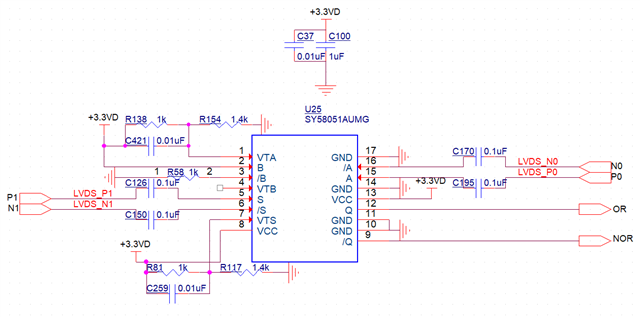

1. 我这里可以给出tlv3801的原理图设计电路,以及其下一级原理图电路。测试结果显示输出共模电压应该是没问题的,大概在1.25V左右,就是摆幅出现问题。TLV3801驱动的下一级是SY58051AU。它们之间互联采用AC耦合,耦合电容是0.1uF。之前测试结果是直接使用示波器测量TLV3801的输出引脚OUT+/-。

2、AC耦合是指TLV3801的输出与下一级互联的时候采样AC耦合,从给出的原理图上可以看到。你所谓的是“偏置电路”是指TLV3801的输出OUT+/-上需要施加偏置?

Amy,

1. 蓝色波形是正常的,所谓“干扰很大”是因为示波器该通道刻度很小,即20mV,所以相较其余2个通道看上去好像干扰很大。

2. SY58051AU差分输入经过AC耦合进来的,波形形状和耦合电容之前一样,至于共模电压与其偏置有关。

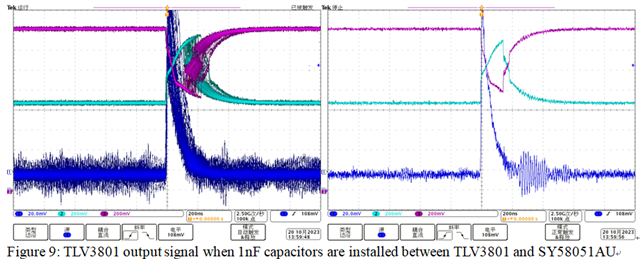

3. 我们确实更换了其它AC耦合电容,比如0.01uF,1nF等,其中0.01uF与0.1uF效果差别不大,使用1nF电容后,OUT+/-的DC偏置不变,但是波形形状有变化,但依然是变形的,如下图所示。

4. 根据SY58051AU手册提供“输入接口应用”图例,我们拆掉AC耦合电容,拆掉VT配置,让AC耦合变成DC耦合形式,这样测量TLV3801输出,结果似乎正常,如下图所示:

5. 拆掉AC耦合电容,让TLV3801与下级OR门(SY58051AU)断开,再给OUT+/-之间装上100欧姆电阻,测量3801输出,其结果与DC耦合类似。

上述4,5似乎说明TLV3801在当前输入情况下运行正常,只是无法与下级或门实现AC耦合互联,我们无法理解为何TLV3801的LVDS输出无法与下一级SY58051AU的CML输入端口实现AC耦合互联?

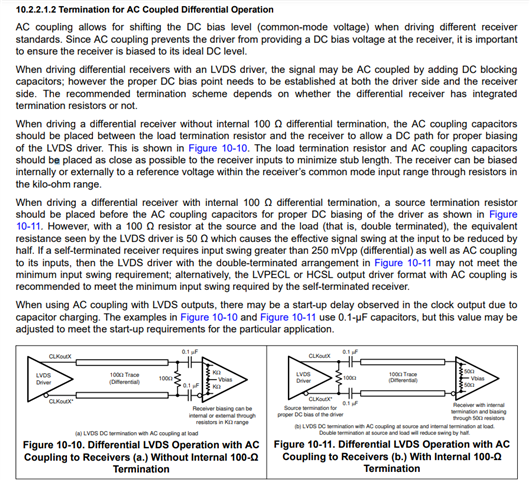

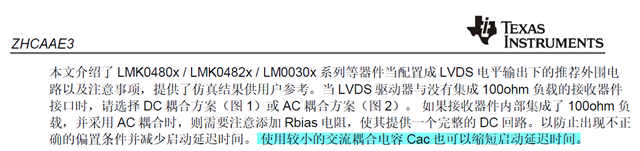

您好很抱歉这份资料我没有找到英文版本的,但是看其最后参考文献是LMK00301/LMK04832 datasheet,您可以查看LMK00301 datasheet 如下截图部分,我感觉这部分写的比较清楚一些,您的情况应该属于截图中的Figure 10-11:

另外,我在很多对应差分互联的时候,从未看到有资料提到这种DC耦合回路问题影响AC耦合,这是为何?一般都是AC耦合直接互联,在接收端添加合适的端接。

如截图中第2段描述: however the proper DC bias point needs to be established at both the driver side and the receiver side. The recommended termination scheme depends on whether the differential receiver has integrated termination resistors or not.即需要在驱动侧和接收器侧建立正确的直流偏压点。 是否可以直接互连取决于驱动器和差分接收器是否具有集成端接电阻。

而TLV3801手册也未给出后级互联的推荐注意事项,我在想TI后续是否可以加入?!

我认为这应该不会加入,因为这是差分接收端需要考虑的事情,如时钟产品 LMK00301/LMK04832,它们是差分接收端,它们的datasheet中有相关内容。

我不知道我上个回复中LMK00301 datasheet 截图内容您是否研读了,我认为它就详细说明了您电路出现上述现象的原因。

在AC耦合时需要在驱动侧和接收侧都建立正确的直流偏压点,推荐的端接方式取决于差分接收器是否具有集成端接电阻。

在您的应用中接收器内部是集成了两个50Ω电阻器的,并且还有直流偏压,因此属于描述的第二种情况,即Figure 10-11,应像Figure 10-11这样连接您的电路,即在交流耦合电容器前面放置一个源端接电阻,以使驱动器(在您的应用中驱动器就是TLV3801)的直流偏置正确。这样源端或说驱动端和负载处都有一个100Ω Ω 电阻,LVDS驱动器看到的等效电阻即为50Ω ,这会导致输入处的有效信号摆幅减少一半,就会导致不满足接收器输入摆幅要求,看您截图输入摆幅最低200mVpp。

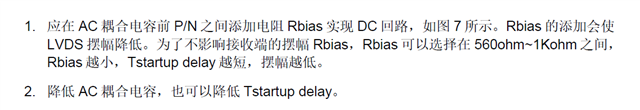

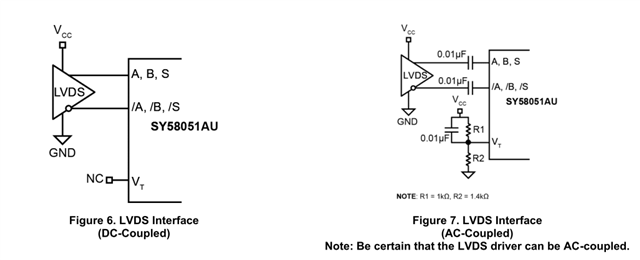

之前附的文档(LMK时钟 family LVDS输出交流耦合设计注意事项)如下截图也有说:Rbias 的添加会使LVDS 摆幅降低。为了不影响接收端的摆幅Rbias,Rbias 可以选择在560ohm~1Kohm 之间。

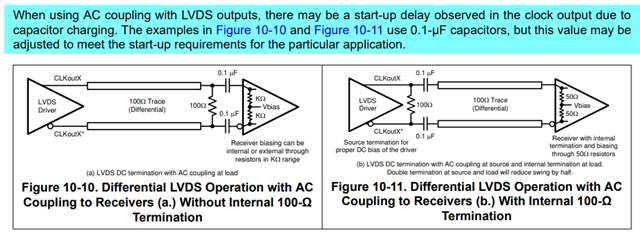

另外还有一个start-up delay的问题,LMK00301 datasheet 仅在Figure 10-11 上方提了一下可以调节AC耦合电容值,如下截图:

LMK时钟 family LVDS输出交流耦合设计注意事项 这个文档的3.1 部分有 对Rbias 不同取值进行仿真,也提到了使用较小的AC耦合电容可以缩短start-up delay时间:

Amy 你好,

非常感谢你的详细答复,我也算彻底明白我们电路LVDS驱动CML时AC耦合情况出现问题的原因。同时我们在此基础上还存在几个疑惑:

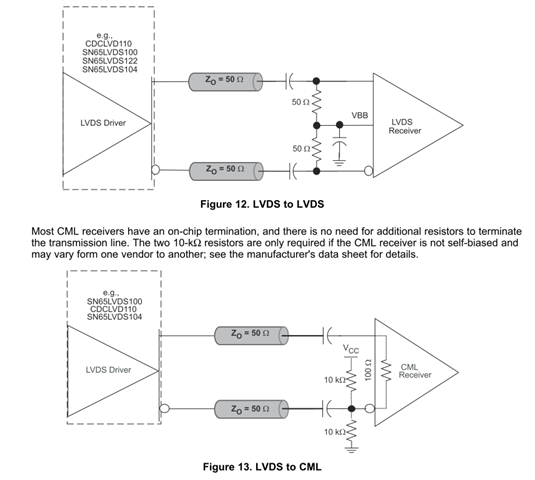

1. LM00301给出答案毕竟是针对此芯片,而TLV3801是否有同样的问题及需求呢?我们在设计电路的时候是参考了TI的文章“AC-CouplingBetweenDifferentialLVPECL,LVDS,HSTL, andCML”,该文给出几个LVDS作为驱动器时的实例,如下图所示,这几个例子LVDS驱动端并未并接电阻,为何?

2. 我们给TVL3801设计当前的电路,除了参考上述实例,也参考了接收侧SY58051AU给出的输入接口实例,如下图,这个实例与上述TI文章给出的实例雷同,我们也查阅大量资料,给出的参考接法都很类似。所以,我们在不明白的是,为何TI会给出在AC耦合下,因为阻止了DC回路,所以需要在驱动侧添加100欧并联端接?

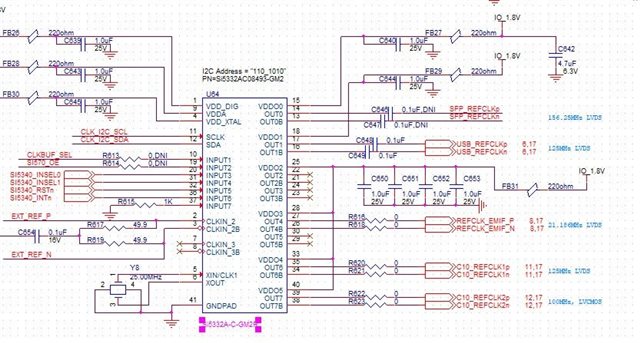

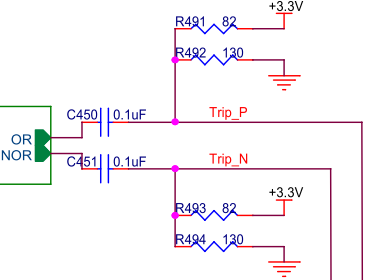

3. 另外一个实例是我们其它板子上使用了其它厂家的时钟分配器件,其输出也是LVDS差分标准,我们使用AC耦合的时候确实是直接简单串接AC耦合电容,如下图所示,输出侧并未在P/N之间并接电阻。是否这类连接中,驱动器中已经涵盖了(或者芯片内部内置了)该并接阻抗?而TI的芯片内部并未内置此阻抗?

4. 最后一个关键性问题,诚如你所说,AC耦合下驱动端并接阻抗,会带来“启动延迟”,如何理解这个启动延迟?是指只在上电瞬间产生的延迟吗?你知道我们使用的是TLV3801,让其作为比较器,也即我们的信号源不是时钟,也非数据,而只是偶合一个单脉冲信号。也即,大部分时间长连0,偶发一个短暂长连1信号。此时“启动延迟”对这些脉冲信号有影响吗?如果启动延迟只是上电瞬间的事情,那么稳定后对我们的系统应该是没有影响的。即只要保证上电后后续脉冲稳定,我们是可以接受的。

1、我查看了下它们都有输出共模电压,或者说有上面提到的DC偏置电压,即在AC耦合时需要在驱动侧和接收侧都需要建立一个直流偏压点。因此不需要再添加上面提到的 Rbias 。

2、这里的主要核心点是“在AC耦合时需要在驱动侧和接收侧都需要建立一个直流偏压点”,因此具体的连接方式取决于驱动侧和接收侧是否集成了这个直流偏置电压,在您的问题中是驱动侧不一样,比较器 TLV3801内部没有直流偏置电压或者说输出共模电压,这个直流偏压一方面是提供了输出共模电压,暗含的另一个意思是给输出提供一个直流回路。而您截图中列出的 SN65LVDS100等内部已经集成了输出共模电压,也就是说已经有了直流回路。我不知道您get到我说的点了没,我认为这是这个问题的核心。

3、是的,是您说的这个问题,主要看内部是否集成了偏置电压,或者说有直流回路。

Amy, 没事。 借此机会能否再请教一个有关CML经AC耦合互联驱动LVPECL的问题?我们的CML驱动器和LVPECL接收器分别位于不同的板子上,所以我们在测量驱动侧的时候是隔离接收侧的。驱动侧如下图所示,驱动器输出经C450,C451两个电容AC耦合出去,为了兼容LVPECL,耦合后由82ohm/130ohm电阻分别对P和N进行端接,端接电平=VCC-1.3=3.3-1.3=2V。实际测量的时候,trig_P与trig_N用万用表测量分别是2.009V和2.005V。我的问题是经过AC耦合差分对的P/N分别偏置到了相同的DC水平,这好像有点不对吧?差分信号,P和N应该位于不同的DC水平吧,它们之间不同的电压中心就是差分对的共模电位才对吧?

通过示波器测量Trig_P与Trig_N果然得出下面这样的信号,AC耦合后的差分对P/N的DC相等,为何?

很抱歉,因为我前几天休假的原因现在才回复您。

你知道我们使用的是TLV3801,让其作为比较器,也即我们的信号源不是时钟,也非数据,而只是偶合一个单脉冲信号。

因为您应用的信号是低频信号,您是否可以尝试将耦合电容增加到 200nF or 500nF,再看输出波形怎样?