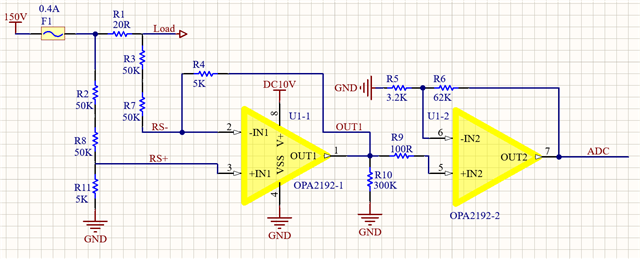

Part Number: OPA2192

有一个150V的DC电源,输出电流0-150mA,想在高侧端测量电源的输出电流,想采用如下电路:采样电阻20欧姆,

OPA2192的V+接10V,part1部分形成一个类似分压的作用,part2部分再放大20倍,再送入ADC,

目前的问题是,Load端空载时,RS+是7.17V,RS-是7.2V,OUT1输出0.006V,ADC端输出0.12V

问题1:为什么空载时,RS-的电压比RS+的电压高? 按照虚短虚断计算,不是应该电压一样么?

问题2:150V电源输出0-15mA时,ADC端输出电压不变,要超过15mA以上,ADC端的电压才开始升高,如何解决这个问题?