Part Number: TLV9042

客户对芯片的EMIRR IN+这一参数比较关注,我们想在实验室中测试一下,因此关于测试方法有一些疑问:

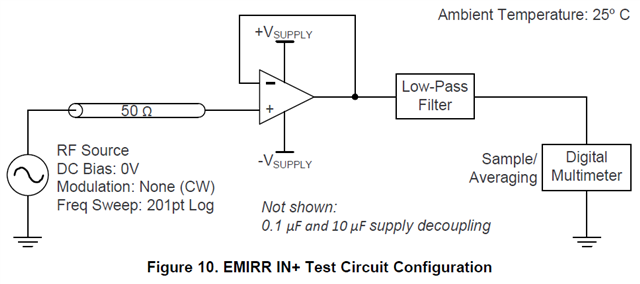

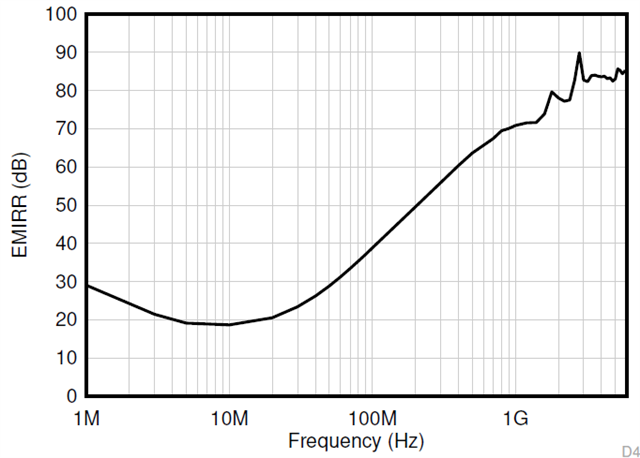

在我们的理解中,测试方法可以简单概括为:将芯片连接成单位负反馈的形式,输入信号给一个AC和DC信号的叠加(这里DC信号为0),在输出端测量DC电压。然后在AC信号为不同频率时,计算出该频率下的EMIRR值,最后在坐标系上描点画出曲线。

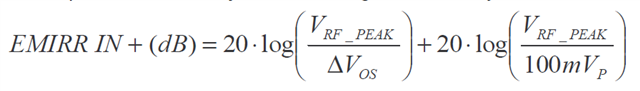

问题1:公式中的ΔVOS指的是谁呢?

第一种看法是,芯片是存在固有的Offset的。在不接AC信号时,输出端测得一个VOS1=VOUT1-VIN+;在接上AC信号后,测得一个VOS2=VOUT2-VIN+(DC),然后ΔVOS=VOS2-VOS1。

第二种看法是,ΔVOS就是上一条的VOS2,ΔVOS=VOS2=VOUT2-VIN+(DC)。

问题2:公式中的100mVp是指什么,100mV的电压值吗?它从何而来?如果输入的AC信号的峰峰值是50mV,在代入公式进行计算时,这一位置仍然是100m吗?

问题3:测试连接图中的低通滤波器是指芯片中固有的,还是另外添加的?它是怎样的结构?截止频率应当是多少?如果是额外添加的,它实际上会更加改善最终的EMIRR结果,为什么额外添加而不是仅测试芯片本身的性能?

问题4:最终的EMIRR曲线是描点描出来的吗?在1MHz AC信号输入时用数字万用表测一次Offset,在2M时测一次,3M时测一次……一直到在6G时测一次Offset,将所有Offset代入公式求出每个频率的EMIRR,最后作图得到曲线吗?这样的话即使使用自动化测试,测试流程也会非常繁琐耗时。