各位大神好:

之前采购了TI的ISO7741FDW的这款芯片,我们现在应用于SiC驱动板,但是在做脉冲群EFT实验时遇到点问题,麻烦帮忙分析下,谢谢。

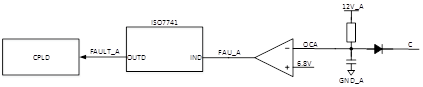

下图是相应该部分的结构图。

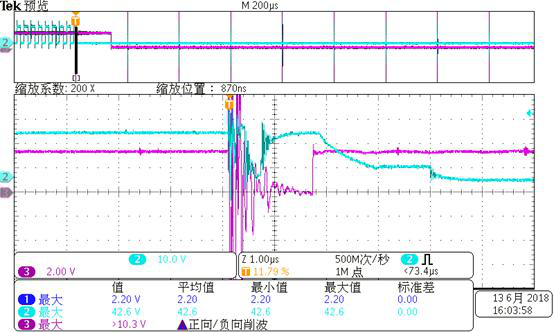

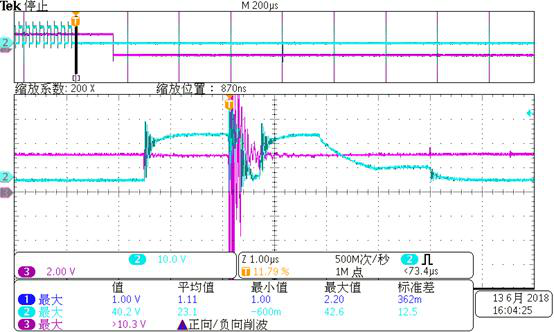

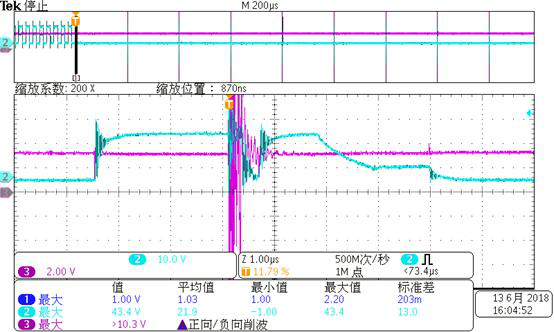

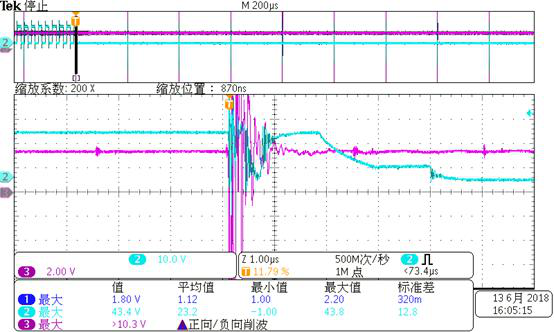

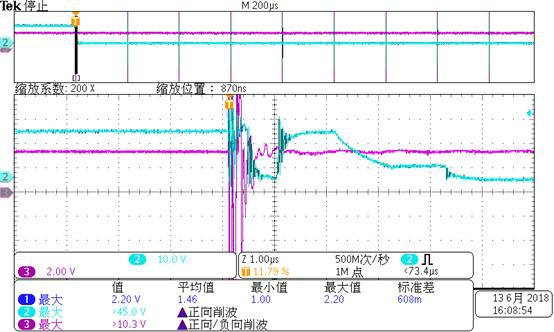

在做EFT时,测得各波形如下所示。

1.原边FAULT_A(3通道)与相应门极输出(2通道)

2.次边FAU_A(3通道)与相应门极输出(2通道)

3.原边3.3V电源(3通道)与相应门极输出(2通道)

4.次边5V电源(3通道,相对门极的地,芯片地相对门极地为-2V)与相应门极输出(2通道)

5.原边使能端(3通道)与相应门极输出(2通道)

从上面几幅图可以看出,传入到ISO7741F的信号FAU_A在EFT时并未拉低,但是从ISO7741F传出的FAULT_A则出现了一段时间的低电平,请问这部分问题是什么原因造成的?我这边暂时还没有找到原因,所以想请教一下。

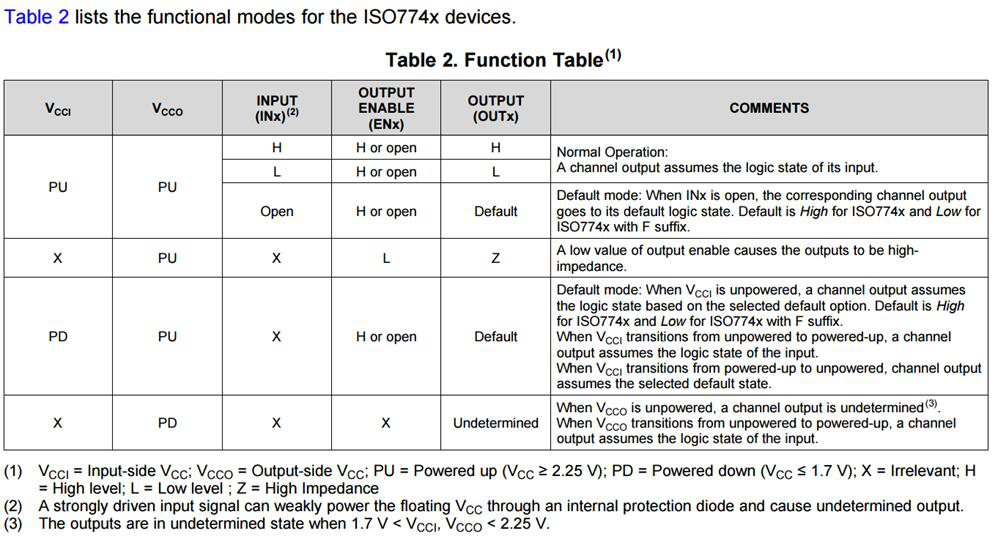

下图是ISO7741F规格书中的一部分,可用于参考。