你好:

我在使用AWR1843的MRR demo工程时,想通过LVDS传输数据,

分别在mss_main.c和mrr_config_consts.h 里面把 define USE_LVDS_INTERFACE_FOR_OBJECT_DATA_TX这个语句给打开

但后者的下面有句注释:

//NOTE: NOT CURRENTLY SUPPORTED

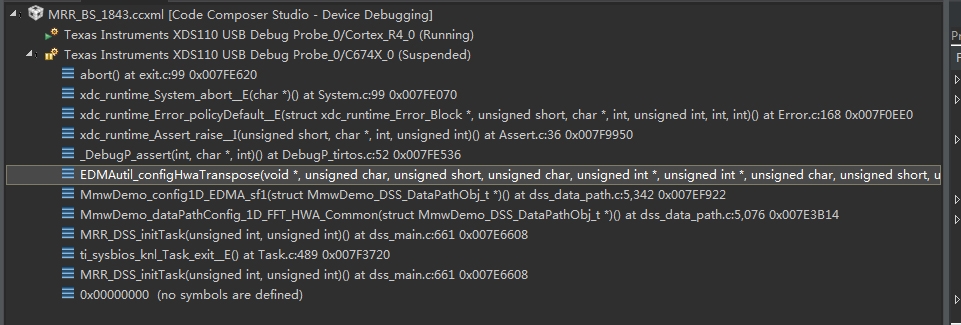

调试的时候报错:

{module#8}: "../config_edma_util_hwa.c", line 203: error {id:0x10000, args:[0x81d8dc, 0x81d8dc]}

同样的环境下,我使用MMW demo就可以顺利使用LVDS

请问,MRR demo是需要额外配置edma 或者其他操作吗?还是现在的版本还不能使用LVDS?

急需得到帮助,感谢

mrr_config_consts.h里面的代码如下:

#ifdef USE_LVDS_INTERFACE_FOR_OBJECT_DATA_TX

//NOTE: NOT CURRENTLY SUPPORTED

/*! @brief EDMA configuration table for FFT processing of subframe 0 */

/** @{*/

//#define MRR_SF0_EDMA_CH_1D_IN_PING EDMA_TPCC1_REQ_FREE_0

//#define MRR_SF0_EDMA_CH_1D_IN_PONG EDMA_TPCC1_REQ_FREE_1

//#define MRR_SF0_EDMA_CH_1D_OUT_PING EDMA_TPCC1_REQ_FREE_2

//#define MRR_SF0_EDMA_CH_1D_OUT_PONG EDMA_TPCC1_REQ_FREE_3

#define MRR_SF0_EDMA_CH_2D_IN_PING EDMA_TPCC1_REQ_FREE_4

#define MRR_SF0_EDMA_CH_2D_IN_PONG EDMA_TPCC1_REQ_FREE_5

#define MRR_SF0_EDMA_CH_DET_MATRIX EDMA_TPCC1_REQ_FREE_6

#define MRR_SF0_EDMA_CH_DET_MATRIX2 EDMA_TPCC1_REQ_FREE_7

#define MRR_SF0_EDMA_CH_3D_IN_PING EDMA_TPCC1_REQ_FREE_8

#define MRR_SF0_EDMA_CH_3D_IN_PONG EDMA_TPCC1_REQ_FREE_9

/** @} */

/*! @brief EDMA configuration table for FFT processing of subframe 1. */

/** @{*/

//#define MRR_SF1_EDMA_CH_1D_IN_PING EDMA_TPCC1_REQ_FREE_10

//#define MRR_SF1_EDMA_CH_1D_IN_PONG EDMA_TPCC1_REQ_FREE_11

//#define MRR_SF1_EDMA_CH_1D_OUT_PING EDMA_TPCC1_REQ_FREE_12

//#define MRR_SF1_EDMA_CH_1D_OUT_PONG EDMA_TPCC1_REQ_FREE_13

#define MRR_SF1_EDMA_CH_2D_IN_PING EDMA_TPCC1_REQ_FREE_14

#define MRR_SF1_EDMA_CH_2D_IN_PONG EDMA_TPCC0_REQ_HWACC_7

#define MRR_SF1_EDMA_CH_DET_MATRIX EDMA_TPCC0_REQ_HWACC_8

#define MRR_SF1_EDMA_CH_DET_MATRIX2 EDMA_TPCC0_REQ_HWACC_9

#define MRR_SF1_EDMA_CH_3D_IN_PING EDMA_TPCC0_REQ_HWACC_10

#define MRR_SF1_EDMA_CH_3D_IN_PONG EDMA_TPCC0_REQ_HWACC_11

/* Only the DSS has access to the interrupts from EDMA

* instance B whereas both the MSS and the DSS can

* access EDMA instance A. We need an EDMA to populate

* the CBUFF through the MSS and hence we use EDMA_INSTANCE_A

* in the MSS and EDMA_INSTANCE_B in the DSS.

*

* The disadvantage is that EDMA_INSTANCE_B (TPCC1) is slower

* by 4x as compared to EDMA_INSTANCE_A (TPCC0). */

#define EDMA_INSTANCE_DSS EDMA_INSTANCE_B

#define EDMA_INSTANCE_MSS EDMA_INSTANCE_A

/** @} */

/*! @brief EDMA configuration table for CBUF. */

/** @{*/

#define MRR_CBUFF_EDMA_CH EDMA_TPCC0_REQ_CBUFF_0

#define MRR_CBUFF_EDMA_SHADOW_CH (EDMA_NUM_DMA_CHANNELS + 0U)

#define CBUFF_EDMA_INSTANCE EDMA_INSTANCE_MSS

/** @}*/

#else

/*! @brief EDMA configuration table for FFT processing of subframe 0 */

/** @{*/

//#define MRR_SF0_EDMA_CH_1D_IN_PING EDMA_TPCC0_REQ_FREE_0

//#define MRR_SF0_EDMA_CH_1D_IN_PONG EDMA_TPCC0_REQ_FREE_1

//#define MRR_SF0_EDMA_CH_1D_OUT_PING EDMA_TPCC0_REQ_FREE_2

//#define MRR_SF0_EDMA_CH_1D_OUT_PONG EDMA_TPCC0_REQ_FREE_3

#define MRR_SF0_EDMA_1D_PING_CH_ID EDMA_TPCC0_REQ_HWACC_0

#define MRR_SF0_EDMA_1D_PONG_CH_ID EDMA_TPCC0_REQ_HWACC_1

#define MRR_SF0_EDMA_1D_PING_SHADOW_LINK_CH_ID EDMA_SHADOW_LNK_PARAM_BASE_ID

#define MRR_SF0_EDMA_1D_PONG_SHADOW_LINK_CH_ID (EDMA_SHADOW_LNK_PARAM_BASE_ID + 1)

#define MRR_SF0_EDMA_1D_PING_CHAIN_CH_ID EDMA_TPCC0_REQ_FREE_0

#define MRR_SF0_EDMA_1D_PONG_CHAIN_CH_ID EDMA_TPCC0_REQ_FREE_1

#define MRR_SF0_EDMA_1D_PING_ONE_HOT_SHADOW_LINK_CH_ID (EDMA_SHADOW_LNK_PARAM_BASE_ID + 2)

#define MRR_SF0_EDMA_1D_PONG_ONE_HOT_SHADOW_LINK_CH_ID (EDMA_SHADOW_LNK_PARAM_BASE_ID + 3)

#define MRR_SF0_EDMA_XFR_COMPLETE_CODE_1D_DONE MRR_SF0_EDMA_1D_PONG_CHAIN_CH_ID

#define MRR_SF0_EDMA_CH_2D_IN_PING EDMA_TPCC0_REQ_FREE_4

#define MRR_SF0_EDMA_CH_2D_IN_PONG EDMA_TPCC0_REQ_FREE_5

#define MRR_SF0_EDMA_CH_DET_MATRIX EDMA_TPCC0_REQ_HWACC_8

#define MRR_SF0_EDMA_CH_DET_MATRIX2 EDMA_TPCC0_REQ_HWACC_9

#define MRR_SF0_EDMA_CH_3D_IN_PING EDMA_TPCC0_REQ_HWACC_10

#define MRR_SF0_EDMA_CH_3D_IN_PONG EDMA_TPCC0_REQ_HWACC_11

/** @} */

/*! @brief EDMA configuration table for FFT processing of subframe 1. */

/** @{*/

//#define MRR_SF1_EDMA_CH_1D_IN_PING EDMA_TPCC0_REQ_FREE_10

//#define MRR_SF1_EDMA_CH_1D_IN_PONG EDMA_TPCC0_REQ_FREE_11

//#define MRR_SF1_EDMA_CH_1D_OUT_PING EDMA_TPCC0_REQ_FREE_12

//#define MRR_SF1_EDMA_CH_1D_OUT_PONG EDMA_TPCC0_REQ_FREE_13

#define MRR_SF1_EDMA_1D_PING_CH_ID EDMA_TPCC0_REQ_HWACC_2

#define MRR_SF1_EDMA_1D_PONG_CH_ID EDMA_TPCC0_REQ_HWACC_3

#define MRR_SF1_EDMA_1D_PING_SHADOW_LINK_CH_ID (EDMA_SHADOW_LNK_PARAM_BASE_ID + 4)

#define MRR_SF1_EDMA_1D_PONG_SHADOW_LINK_CH_ID (EDMA_SHADOW_LNK_PARAM_BASE_ID + 5)

#define MRR_SF1_EDMA_1D_PING_CHAIN_CH_ID EDMA_TPCC0_REQ_FREE_2

#define MRR_SF1_EDMA_1D_PONG_CHAIN_CH_ID EDMA_TPCC0_REQ_FREE_3

#define MRR_SF1_EDMA_1D_PING_ONE_HOT_SHADOW_LINK_CH_ID (EDMA_SHADOW_LNK_PARAM_BASE_ID + 6)

#define MRR_SF1_EDMA_1D_PONG_ONE_HOT_SHADOW_LINK_CH_ID (EDMA_SHADOW_LNK_PARAM_BASE_ID + 7)

#define MRR_SF1_EDMA_XFR_COMPLETE_CODE_1D_DONE MRR_SF1_EDMA_1D_PONG_CHAIN_CH_ID

#define MRR_SF1_EDMA_CH_2D_IN_PING EDMA_TPCC0_REQ_FREE_14

#define MRR_SF1_EDMA_CH_2D_IN_PONG EDMA_TPCC0_REQ_HWACC_7

#define MRR_SF1_EDMA_CH_DET_MATRIX EDMA_TPCC0_REQ_HWACC_12

#define MRR_SF1_EDMA_CH_DET_MATRIX2 EDMA_TPCC0_REQ_HWACC_13

#define MRR_SF1_EDMA_CH_3D_IN_PING EDMA_TPCC0_REQ_HWACC_14

#define MRR_SF1_EDMA_CH_3D_IN_PONG EDMA_TPCC0_REQ_HWACC_15

#define MRR_SF0_EDMA_2D_PING_CH_ID EDMA_TPCC0_REQ_HWACC_4

#define MRR_SF0_2D_PING_SHADOW_LINK_CH_ID1 (EDMA_SHADOW_LNK_PARAM_BASE_ID + 8)

//#define MRR_SF0_2D_PING_CHAIN_CH_ID1 EDMA_TPCC0_REQ_FREE_8

//#define MRR_SF0_2D_PING_SHADOW_LINK_CH_ID2 (EDMA_SHADOW_LNK_PARAM_BASE_ID + 9)

#define MRR_SF0_2D_PING_CHAIN_CH_ID2 EDMA_TPCC0_REQ_FREE_9

#define MRR_SF0_2D_PING_SHADOW_LINK_CH_ID3 (EDMA_SHADOW_LNK_PARAM_BASE_ID + 10)

#define MRR_SF0_2D_PING_CHAIN_CH_ID3 EDMA_TPCC0_REQ_FREE_10

#define MRR_SF0_2D_PING_SHADOW_LINK_CH_ID4 (EDMA_SHADOW_LNK_PARAM_BASE_ID + 11)

#define MRR_SF0_EDMA_2D_PONG_CH_ID EDMA_TPCC0_REQ_HWACC_5

#define MRR_SF0_2D_PONG_SHADOW_LINK_CH_ID1 (EDMA_SHADOW_LNK_PARAM_BASE_ID + 12)

//#define MRR_SF0_2D_PONG_CHAIN_CH_ID1 EDMA_TPCC0_REQ_FREE_11

//#define MRR_SF0_2D_PONG_SHADOW_LINK_CH_ID2 (EDMA_SHADOW_LNK_PARAM_BASE_ID + 13)

#define MRR_SF0_2D_PONG_CHAIN_CH_ID2 EDMA_TPCC0_REQ_FREE_12

#define MRR_SF0_2D_PONG_SHADOW_LINK_CH_ID3 (EDMA_SHADOW_LNK_PARAM_BASE_ID + 14)

#define MRR_SF0_2D_PONG_CHAIN_CH_ID3 EDMA_TPCC0_REQ_FREE_13

#define MRR_SF0_2D_PONG_SHADOW_LINK_CH_ID4 (EDMA_SHADOW_LNK_PARAM_BASE_ID + 15)

#define MRR_SF0_EDMA_XFR_COMPLETE_CODE_2D_DONE MRR_SF0_2D_PONG_CHAIN_CH_ID2

/* Use the faster EDMA_INSTANCE_A (TPCC0) in the DSS */

#define EDMA_INSTANCE_DSS EDMA_INSTANCE_A

#define EDMA_INSTANCE_MSS EDMA_INSTANCE_B

/** @} */

/*! @brief EDMA configuration table for CBUF. (Unused in this configuration).*/

/** @{*/

#define MRR_CBUFF_EDMA_CH EDMA_TPCC0_REQ_CBUFF_0

#define MRR_CBUFF_EDMA_SHADOW_CH (EDMA_NUM_DMA_CHANNELS + 0U)

#define CBUFF_EDMA_INSTANCE EDMA_INSTANCE_B