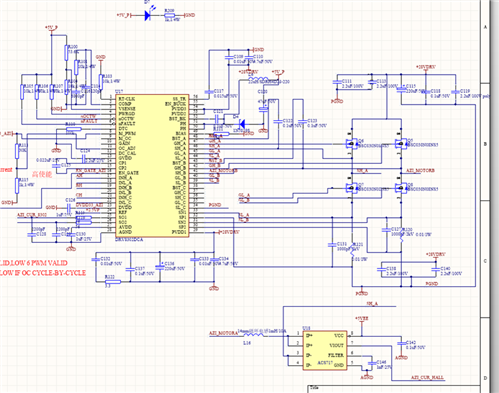

drv8302在使用过程中会概率性出现内部驱动电源GVDD输出为0的情况,此时使用EN_GATE引脚功能失效,对引脚拉低,拉高不能清除芯片报错以及使GVDD重新输出,但是此时测量芯片供电PVDD是正常的。只有重新给芯片的供电重新下电,上电才能使GVDD重新输出,DRV8302的外围电路是按照2011版本的数据手册上的推荐电路设计的。想请教一下出现这种情况,是哪方面的原因引起这种现象的呢?

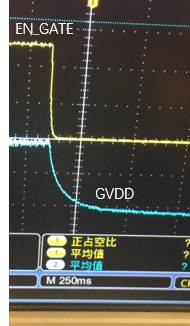

在使用过程中,EN_GATE引脚输入信号加了RC滤波,下面是EN_GATE的波形,是否是使能信号边沿过缓导致的呢?