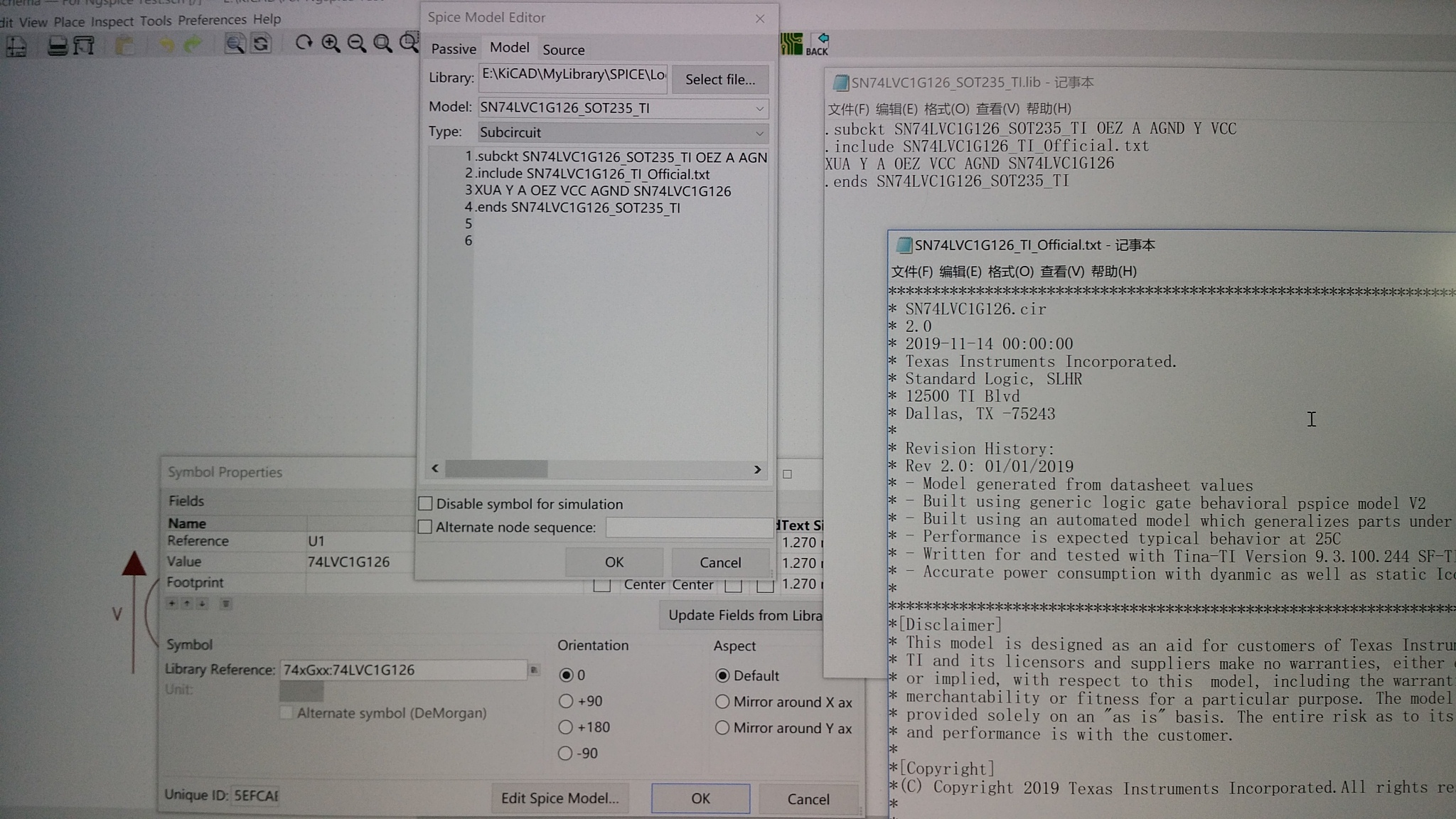

你好,情况是这样的,我常用的仿真平台是电路板设计工具KiCad自带的Ngspice仿真器。首先从TI官方下载了器件的Pspice文件,将它改名为“SN74LVC1G126_TI_Official.txt”,然后再写一个lib文件对官方文件中的器件引脚顺序做调整,以便与KiCad中的封装引脚编号一致,之后命名为“SN74LVC1G126_SOT235_TI.lib”,然后设置电路图中的器件模型,如下图1:

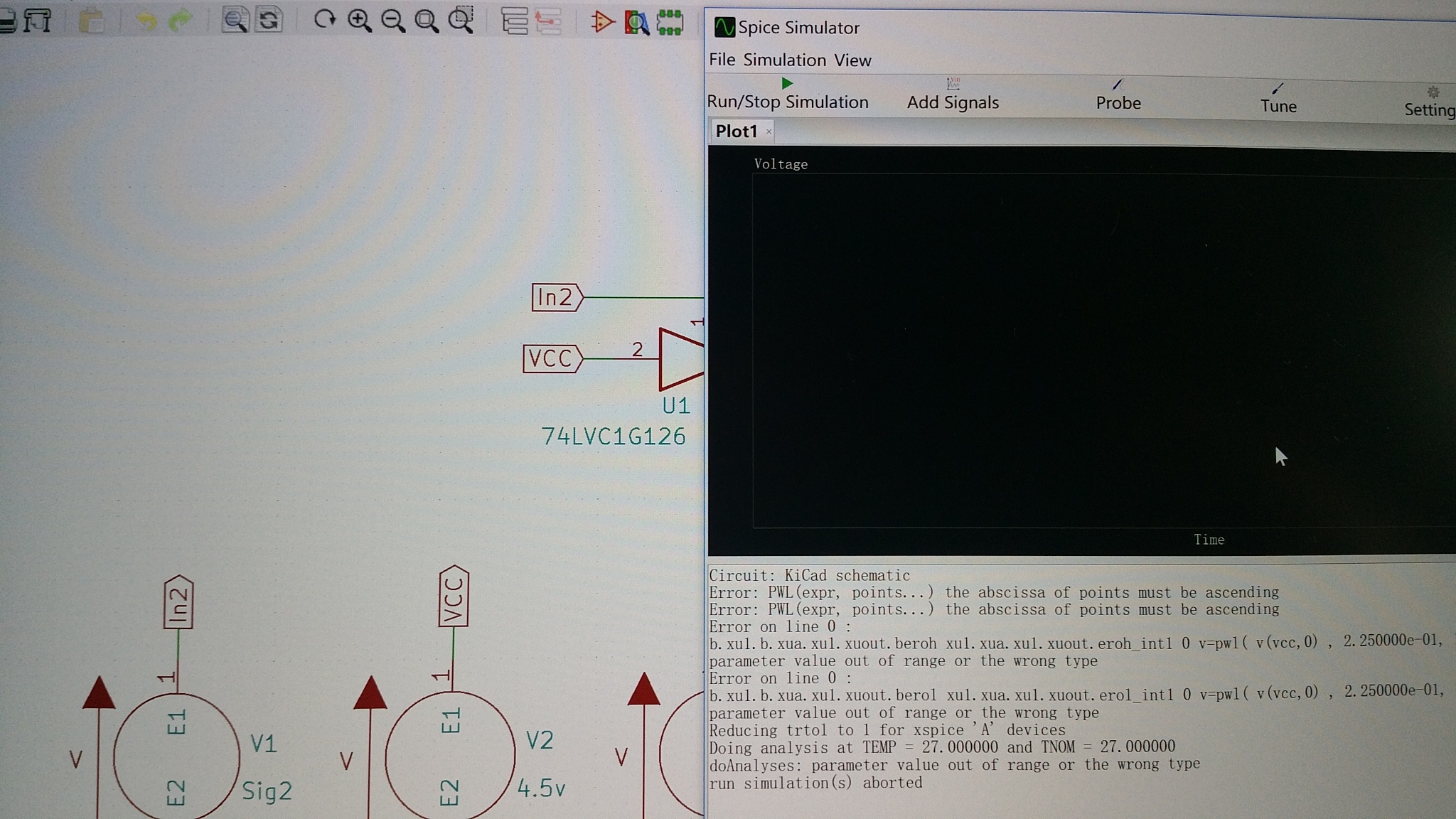

运行第一次仿真,结果直接报错,没有任何结果,如图2:

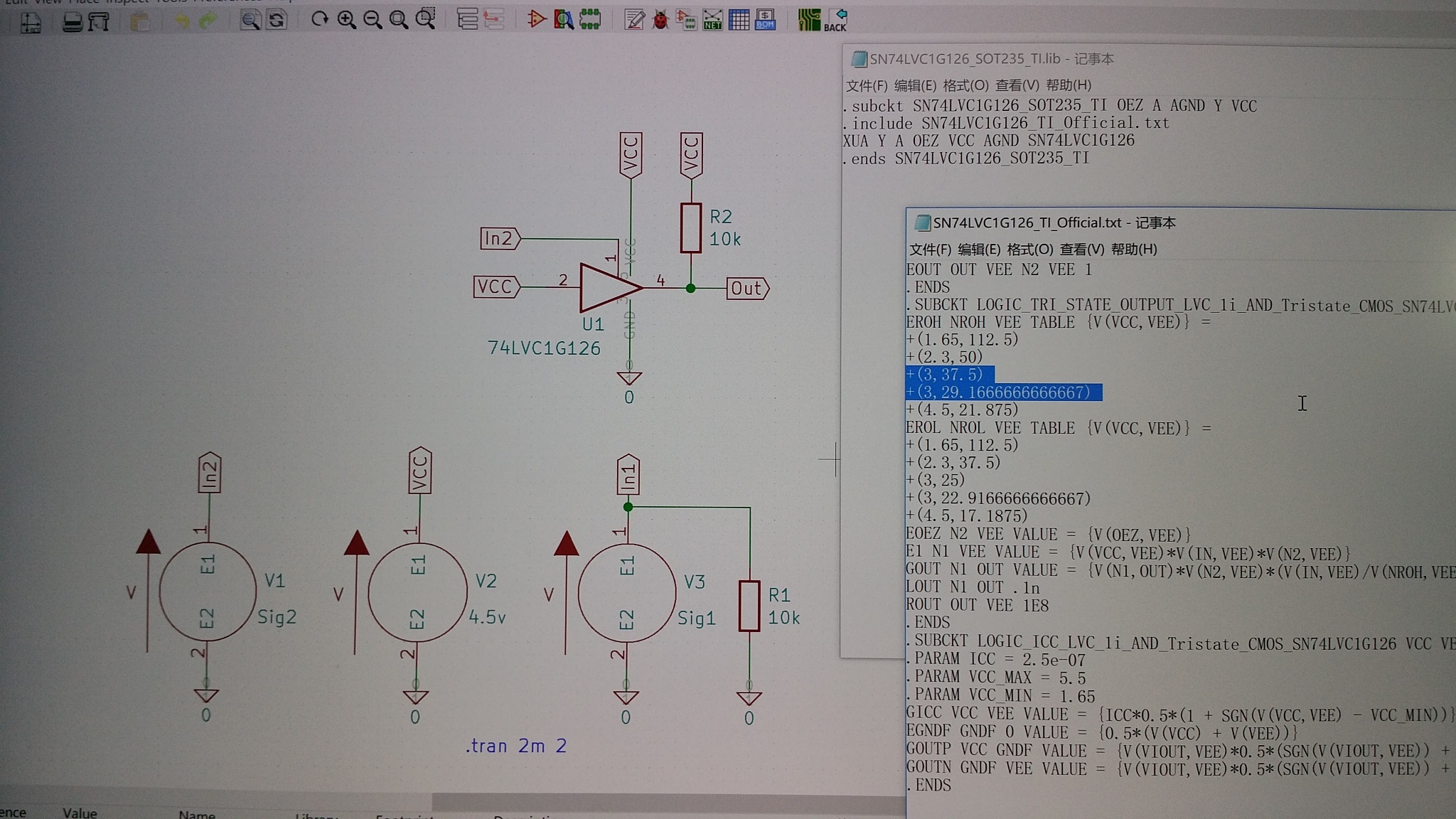

我对Spice文件语法不熟悉,但是根据部分错误提示大致猜到在官方文件中有两处数据可能是有问题的,再结合数据手册,1.65,2.3,3,3,4.5这是一组递增的电压,后面的数据看不懂是什么,但是规律是严格递减的。那么同一个3怎么对应出两个值37.5和29.1666666666667呢?这里会不会是一个笔误?下面那组也一样,从而导致Ngspice出错终止。如图3:

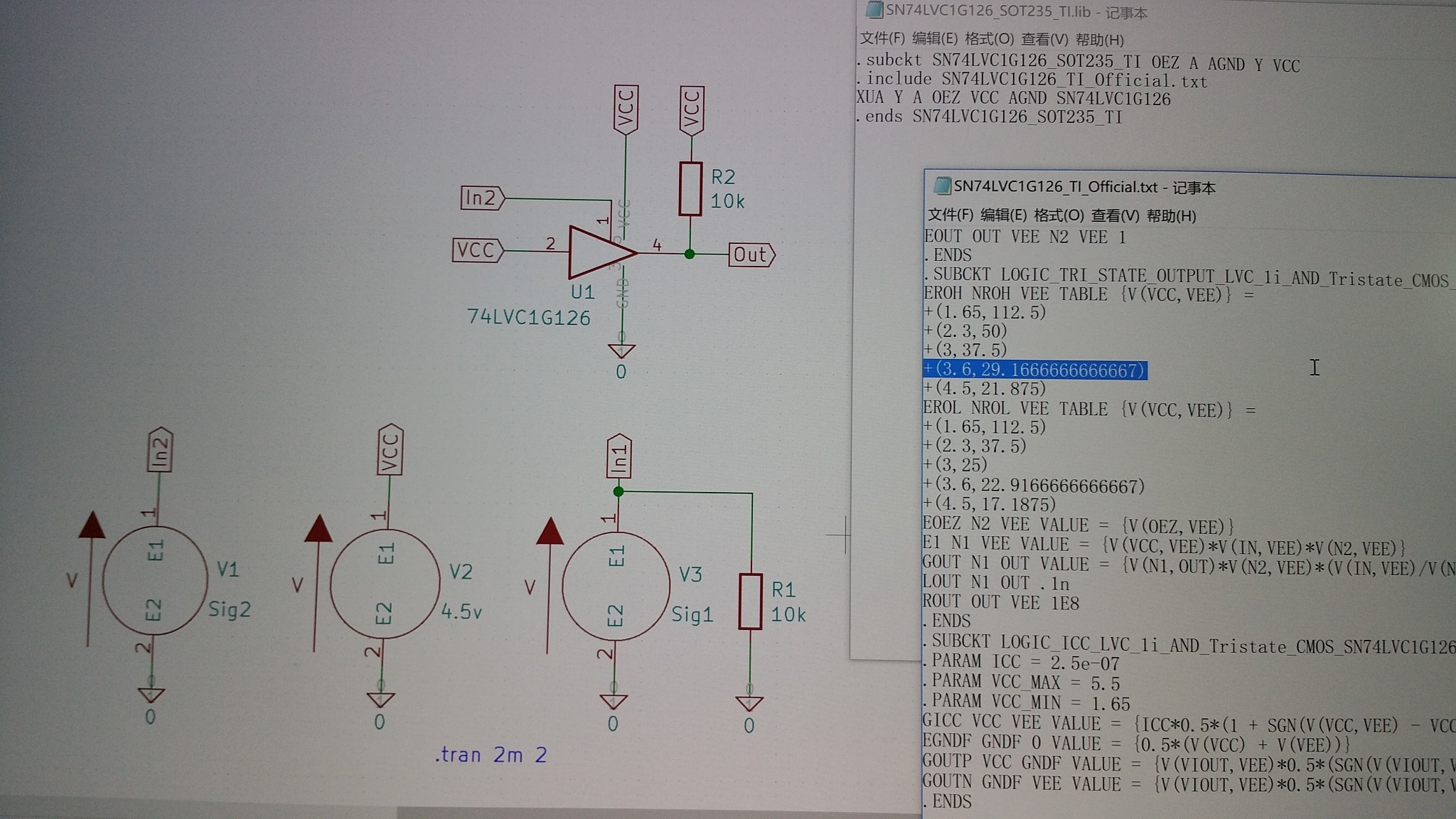

为了让仿真能进行下去,我尝试将后面那个3改成了3.6,两处都改了,如图4:

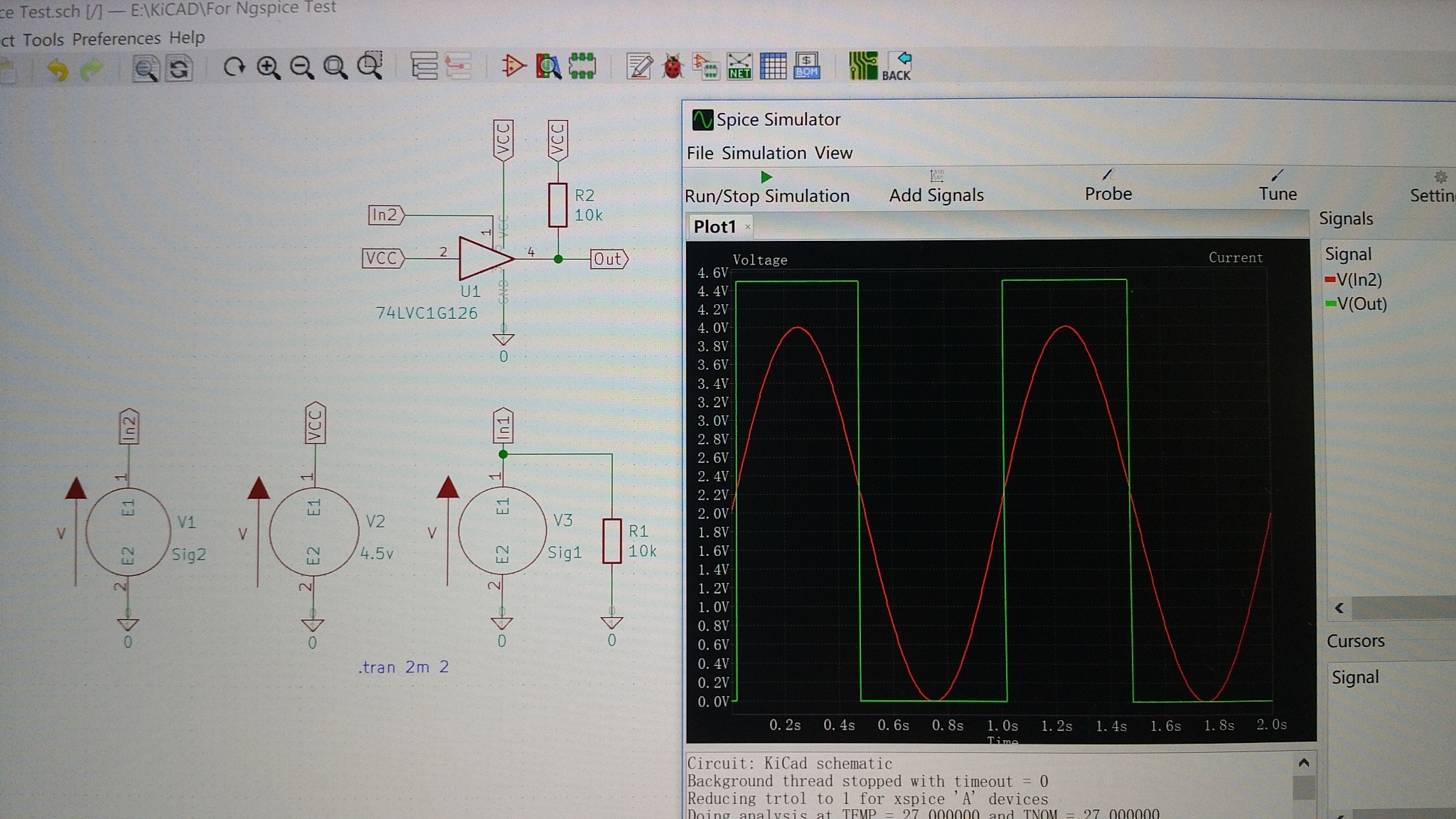

再次运行仿真器,这次通过并得到了一个结果。然而,这个结果是不对的,我特意测试的是高阻态,正确的结果输出应该是值为4.5v的一条水平直线才对。高阻态仿成低电平的效果,跟与门一样了。如图5

不知道问题处在哪里,不过无非三种可能:

1、TI官方的器件模型文件有问题,三态门最重要的高阻态竟然未能正确实现。

2、官方Pspice模型、KiCad和Ngspice三者存在兼容性问题。

3、我的操作或设置方法不正确,使用出错。然而,我用同样的方式测试了SN74LVC1G00、SN74LVC1G02、SN74LVC1G04、SN74LVC1G08、SN74LVC1G14、SN74LVC1G17、SN74LVC1G32这一系列器件的官方Pspice文件,都得到了正确的结果。

实际上我还测试了SN74LVC1G125,结果同样是错的,高阻态成了低电平。

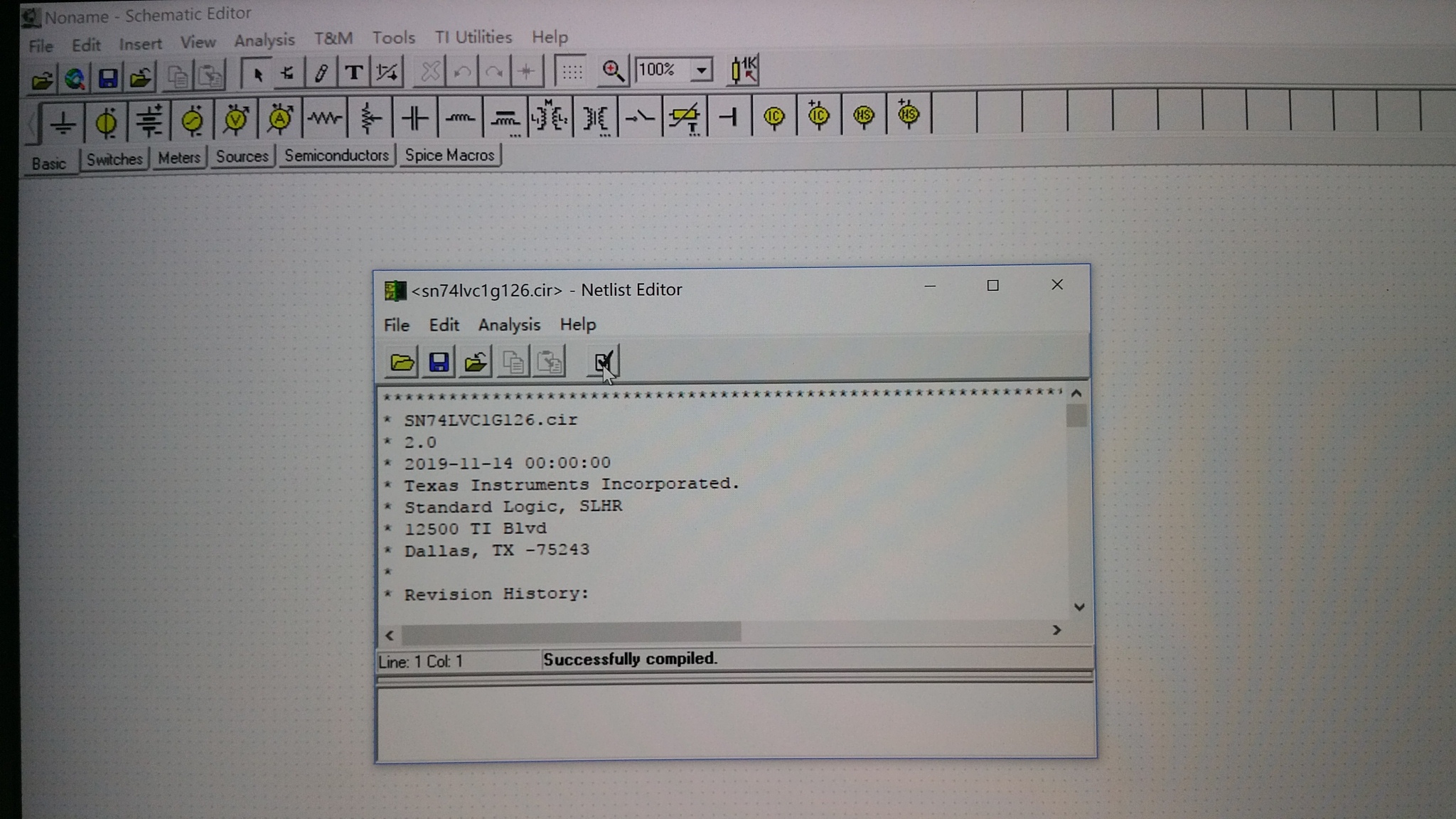

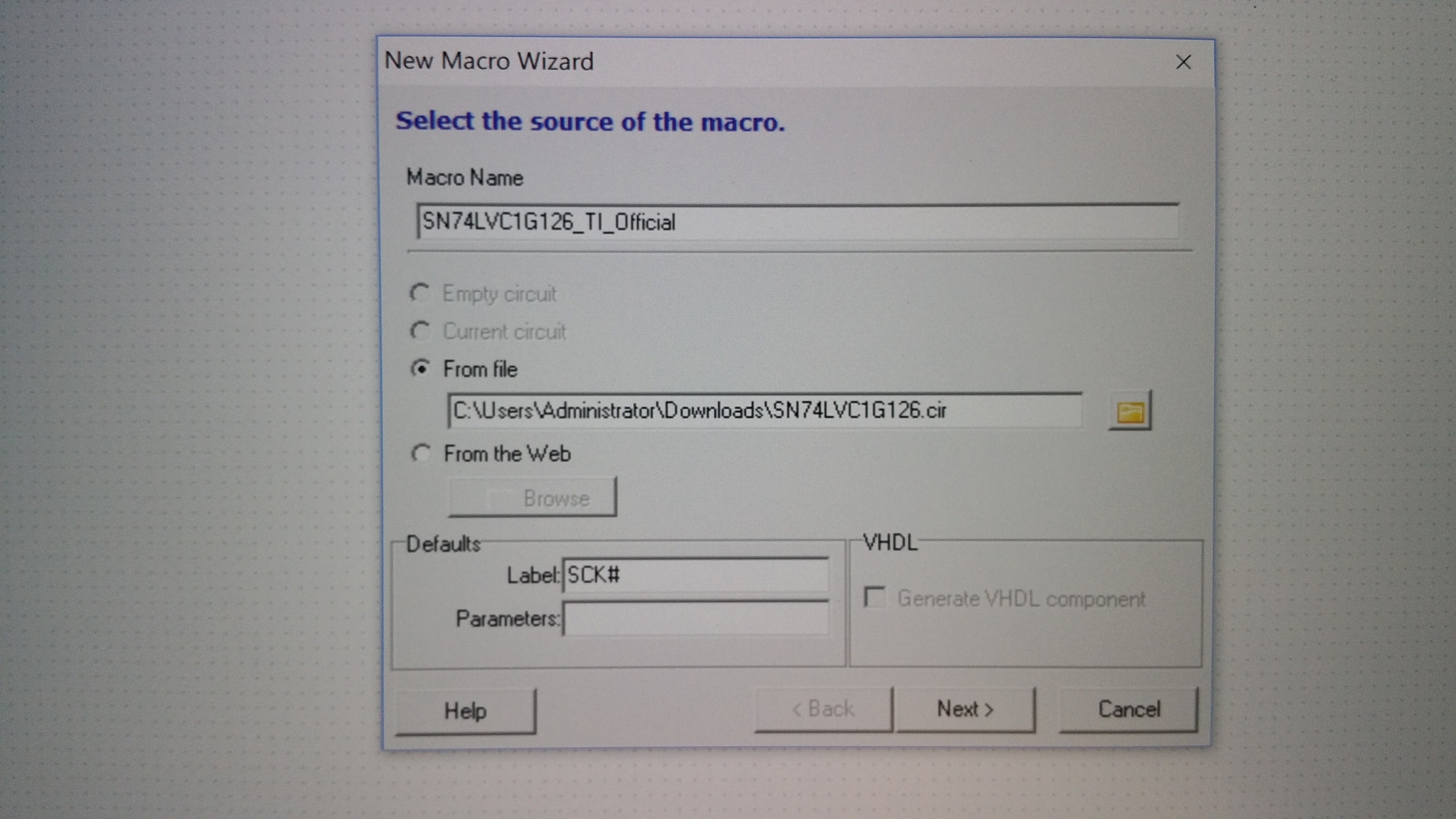

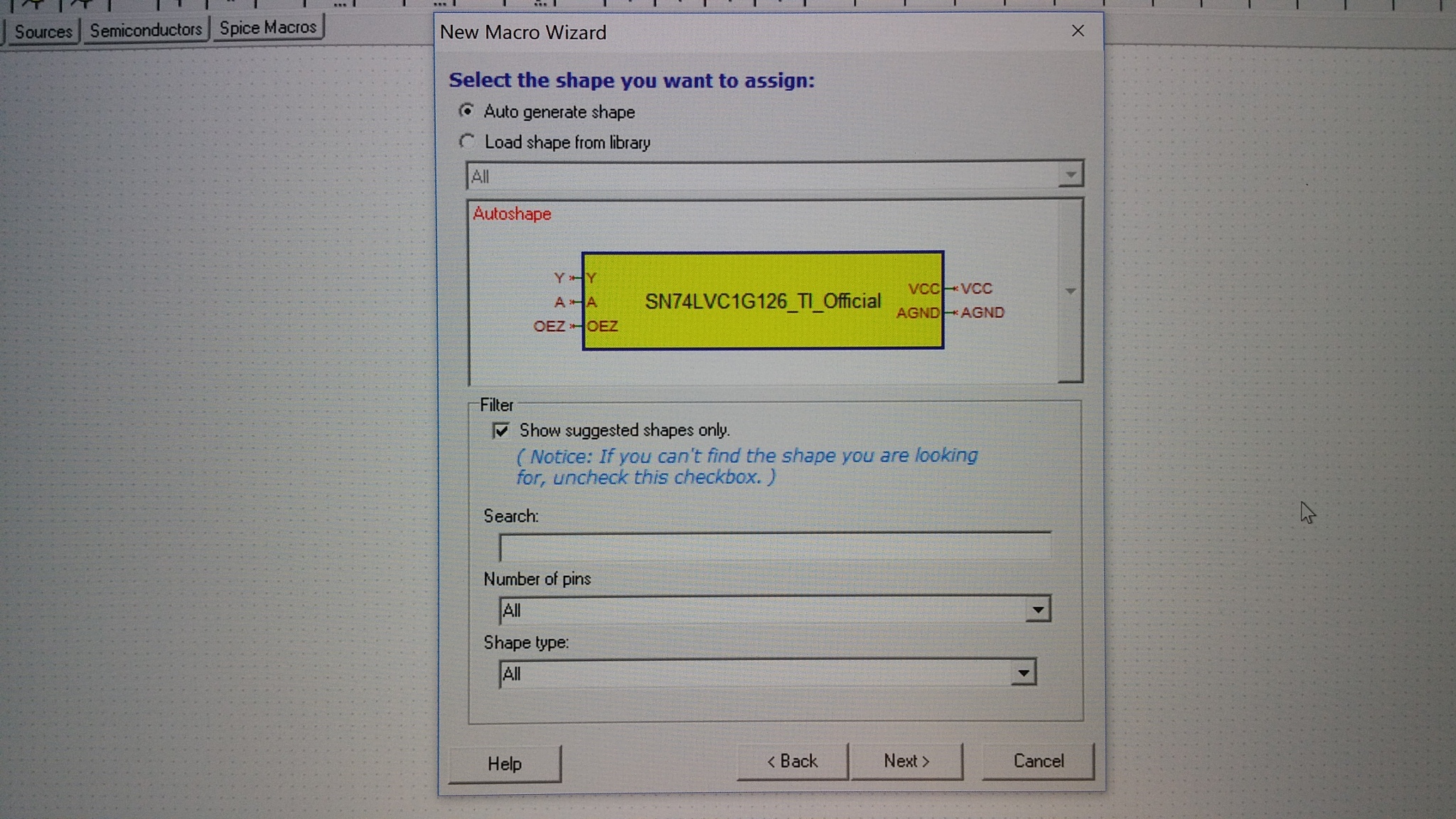

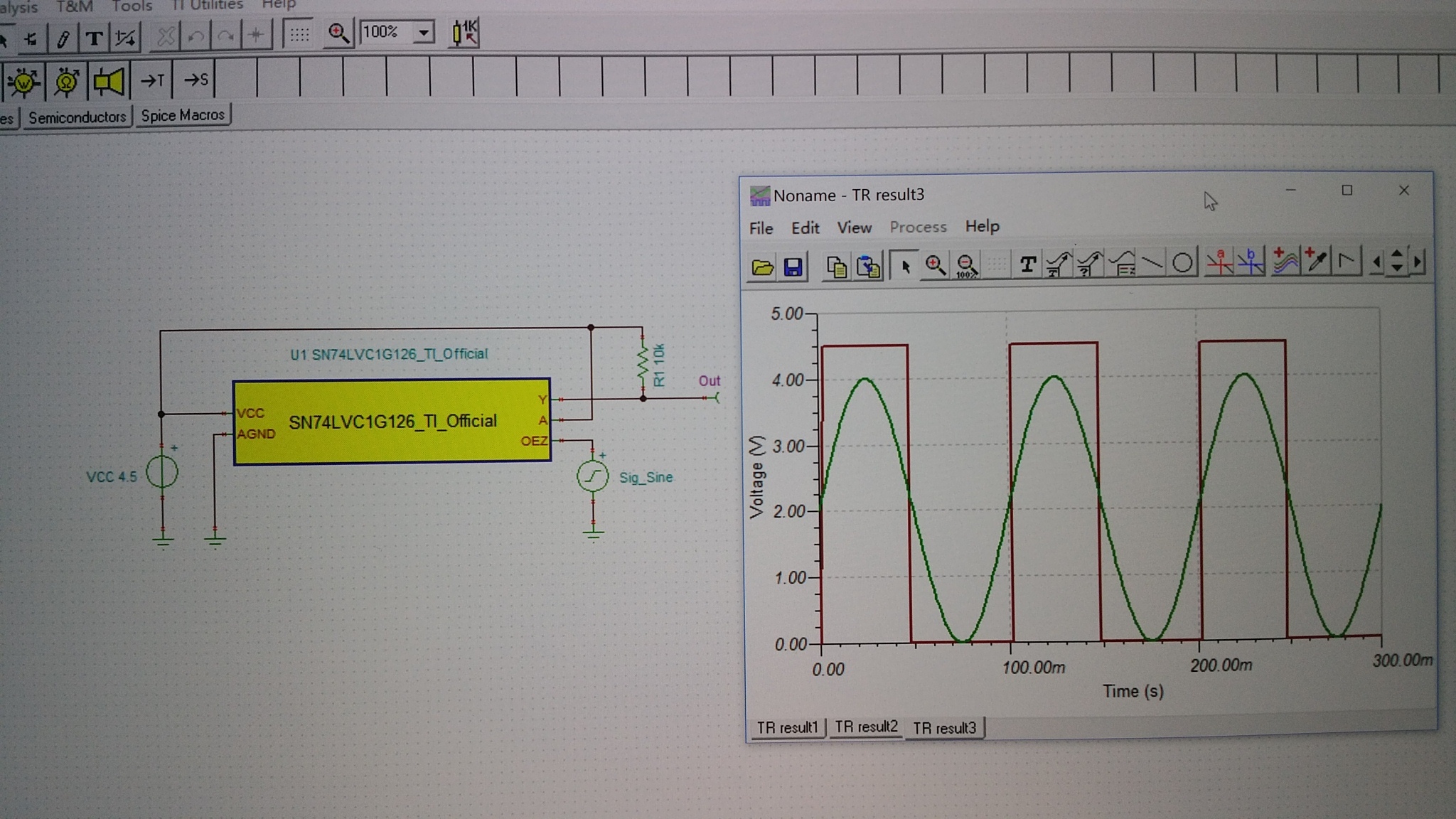

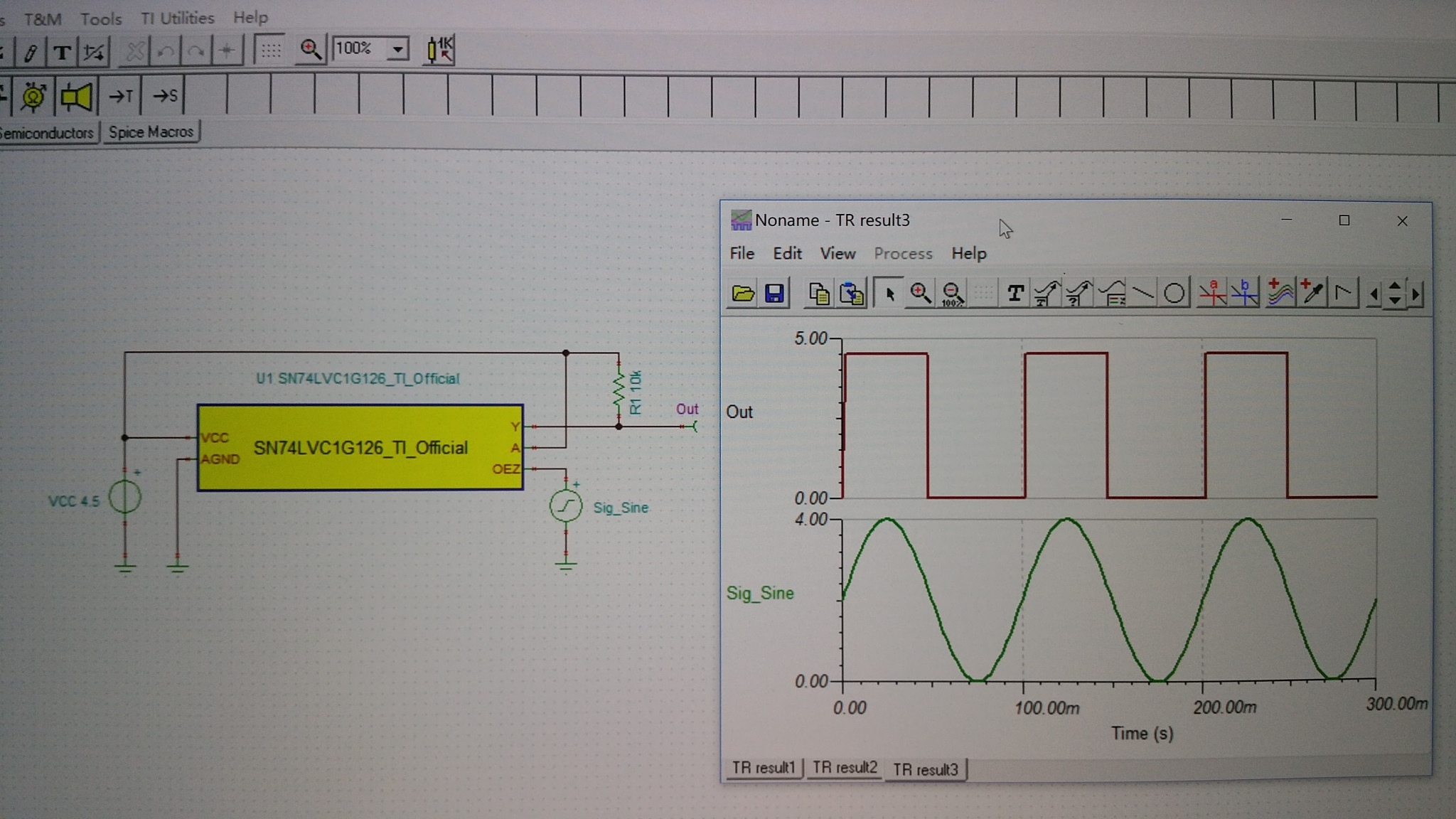

后来我又改用官方的Tina-TI仿真器看看结果,看是不是兼容性问题,不过做出来结果还是一样的,图片在下面,看看操作有什么问题没有,假如不是我的使用出问题,那现在更加怀疑官方发布的器件Pspice模型文件是不是完全正确 ^_^。。

请大家给予指正,谢谢。