Part Number: TPA3136D2

您好,

我正在使用 TPA3136D2,想了解一下它在输出削波期间的占空比行为。

根据数据手册:

9.1 Overview

"These capacitors ensure sufficient energy storage, even during clipped low frequency audio signals, to keep the high-side power stage FET (LDMOS) fully turned on during the remaining part of its ON cycle."

9.3.3 PLIMIT

The PLIMIT circuit sets a limit on the output peak-to-peak voltage. The limiting is done by limiting the duty cycle to a fixed maximum value. The limit can be thought of as a "virtual" voltage rail which is lower than the supply connected to PVCC. The "virtual" rail is approximately four times the voltage at the PLIMIT pin. The output voltage can be used to calculate the maximum output power for a given maximum input voltage and speaker impedance.

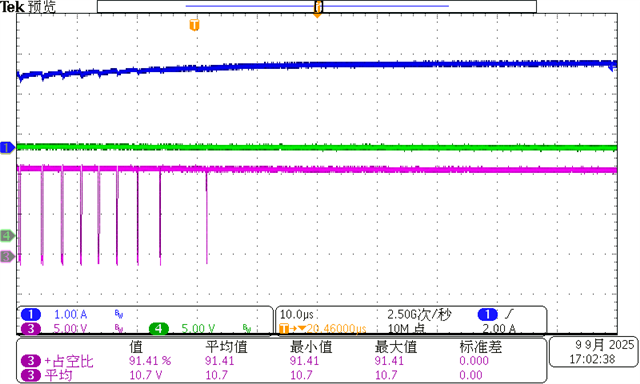

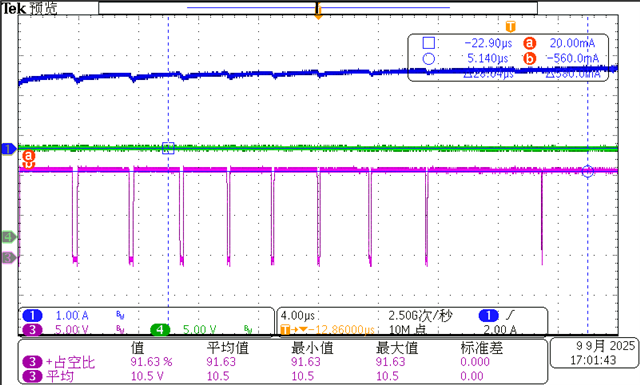

From my measurements, it appears that during clipping, the OUTNL/OUTNR duty cycle can reach 100%. I would like to confirm whether this IC is indeed capable of achieving a full 100% duty cycle.

我的电路配置(不是EVM)如下:

AVCC = 12V

RL = 4Ω

PLIMIT = 1/2*GVDD

BTL 模式 = 单声道 PBTL 模式

扬声器输出功率 = 5W。

附件是三张波形截图(紫色是OUTPL,磁珠前端),显示削波期间占空比接近 100%。有人能确认我的观察是否正确,或者我在这个配置中是否遗漏了什么吗?

提前感谢您的解答!