一个电路中有两片PCM5102A,工作模式:SCK接地(PLL有效)、DEMP接地(De-emphasis:Off)、FLT接地(Filter select : Normal latency)、FMT接高(Audio format selection : Left-justified)、XSMT接高(soft un-mute),两片BCK、LRCK、DATA信号各自并联后被FPGA驱动,输出50Hz的正弦波。

测试发现两片DAC输出的正弦波的相位,不是固定在0°不变,而是在每次重新上电(整个电路掉电再上电)或FPGA复位重启(BCK、LRCK、DATA信号暂停几秒在恢复)后,有可能固定在0°、-0.08°、0.08°(还有其它附近值)等值上,而不是每次重启都为0°。

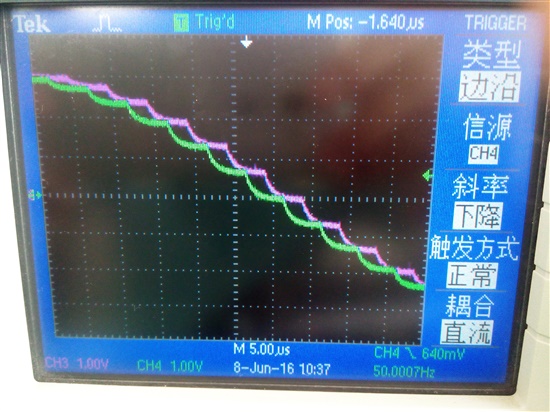

进一步分析测试,当将输出波形设置为50Hz的方波时,用示波器观察两片DAC的输出波形的上升沿和下降沿,可以测量出两者波形并非每次重启后都是完全重合(同相)的,而是每次重启后,两者之间存在的时间差可能固定(一旦重启后就不再变化)在0s、5us、-5us、7us(还有其它附近值)。

分析原因:1.不同芯片内部PLL每一次启动稳定的时间不完全一致造成的?2.芯片的内部延时不是datasheet中所说的20ts,而是不同芯片每次重启后延时时间有一定的变化范围?

请大咖解疑释惑,谢谢!