你好,先说一下我的问题,在调试AIC3254时,发现只要涉及到miniDSP参与的,在我自制的电路板上配置后 HPL, HPR没有输出,在EVM-K评估板上可以正常工作。

实验1 可以说明 我自制电路板的硬件是没有问题的,具体实验如下:

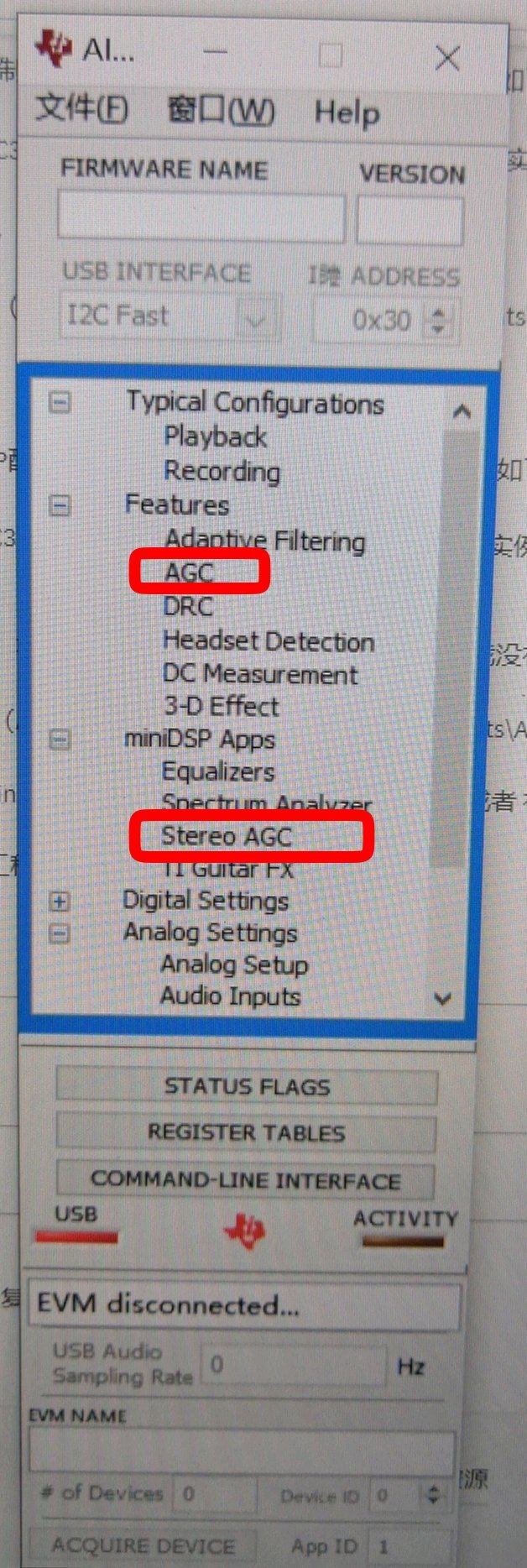

1. 用评估软件 AIC3254 CS 在EVM-K评估板 测试Features里的实例 AGC, 在评估板上 HPL, HPR 输出正常。

2. 用相同的参数,在我自电路板上配置后,输出正常。

3. 配置文件为:(AIC3254 CS目录下的文件 Texas Instruments\AIC3254 CS\DATA\EVM\AIC3254\AGC\AGC_ON_BOARD_DIFF_MIC.txt)

实验2 涉及到miniDSP配置时,自制电路板没有输出,具体实验如下:

1. 用评估软件 AIC3254 CS 在EVM-K评估板 测试miniDSP里的实例 Stereo AGC, 在评估板上 HPL, HPR 输出正常。 用示波器测得 MCLK = 11.2896 MHz

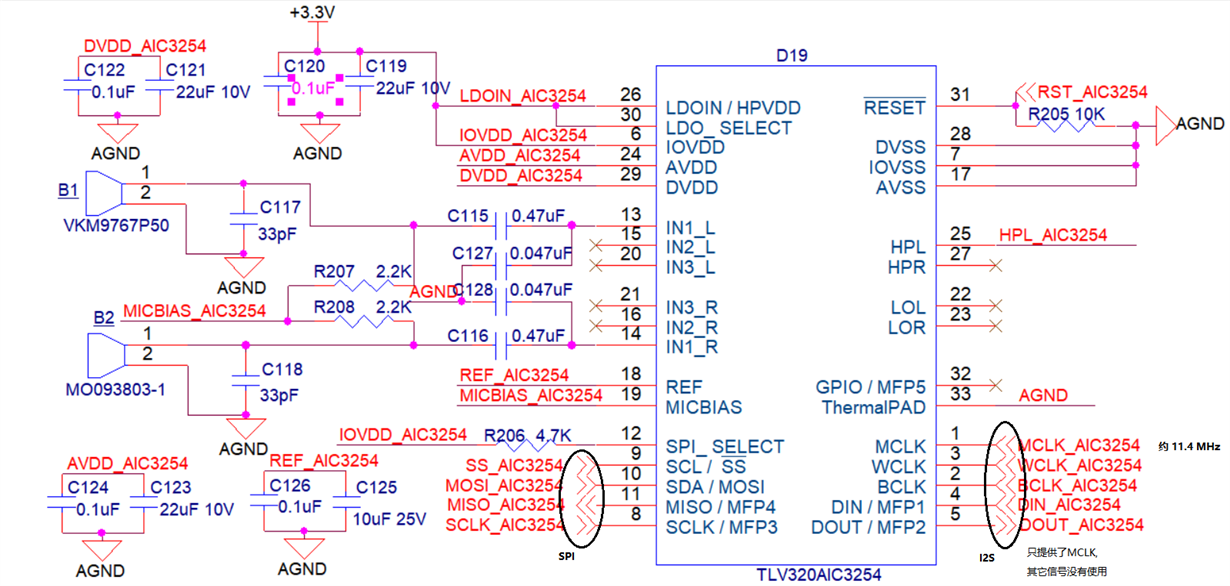

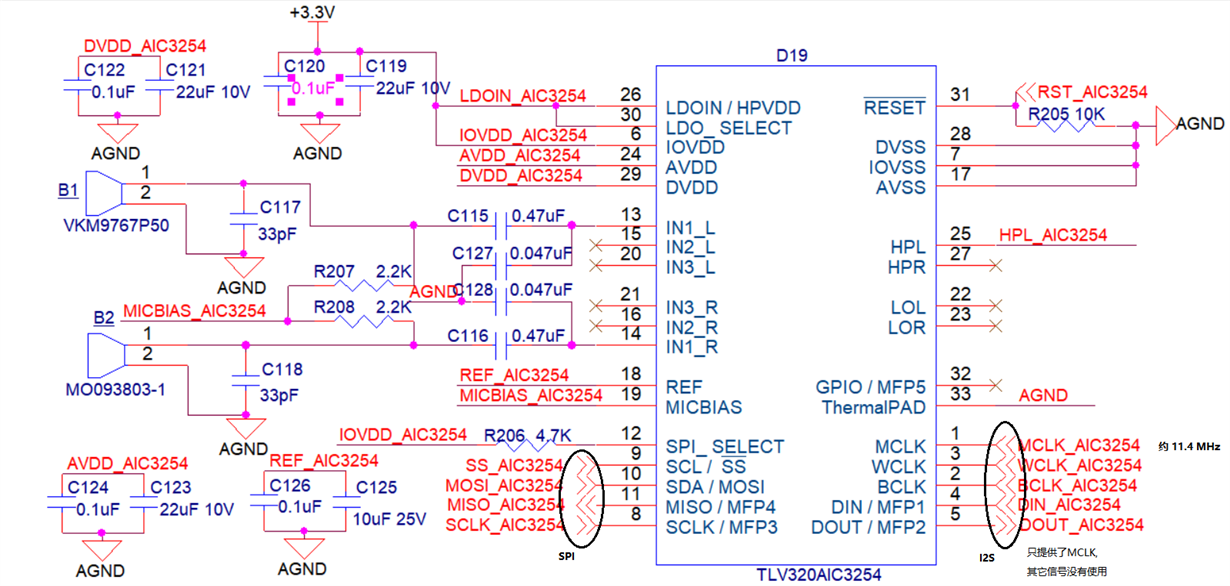

2. 用相同的参数,在我自制电路板上配置后,没有输出。我没有使用I2S接口。自制电路板给的 MCLK 频率为 11.4MHz左右。

3. 配置文件为:(AIC3254 CS目录下的文件 Texas Instruments\AIC3254 CS\DATA\EVM\AIC3254\ST_AGC\ST_AGC.cfg)

想问一下,涉及到miniDSP配置时,需要额外的配置参数吗?或者 有什么特殊需要注意的地方?

希望熟悉AIC3254的工程师帮我解答一下,非常感谢。