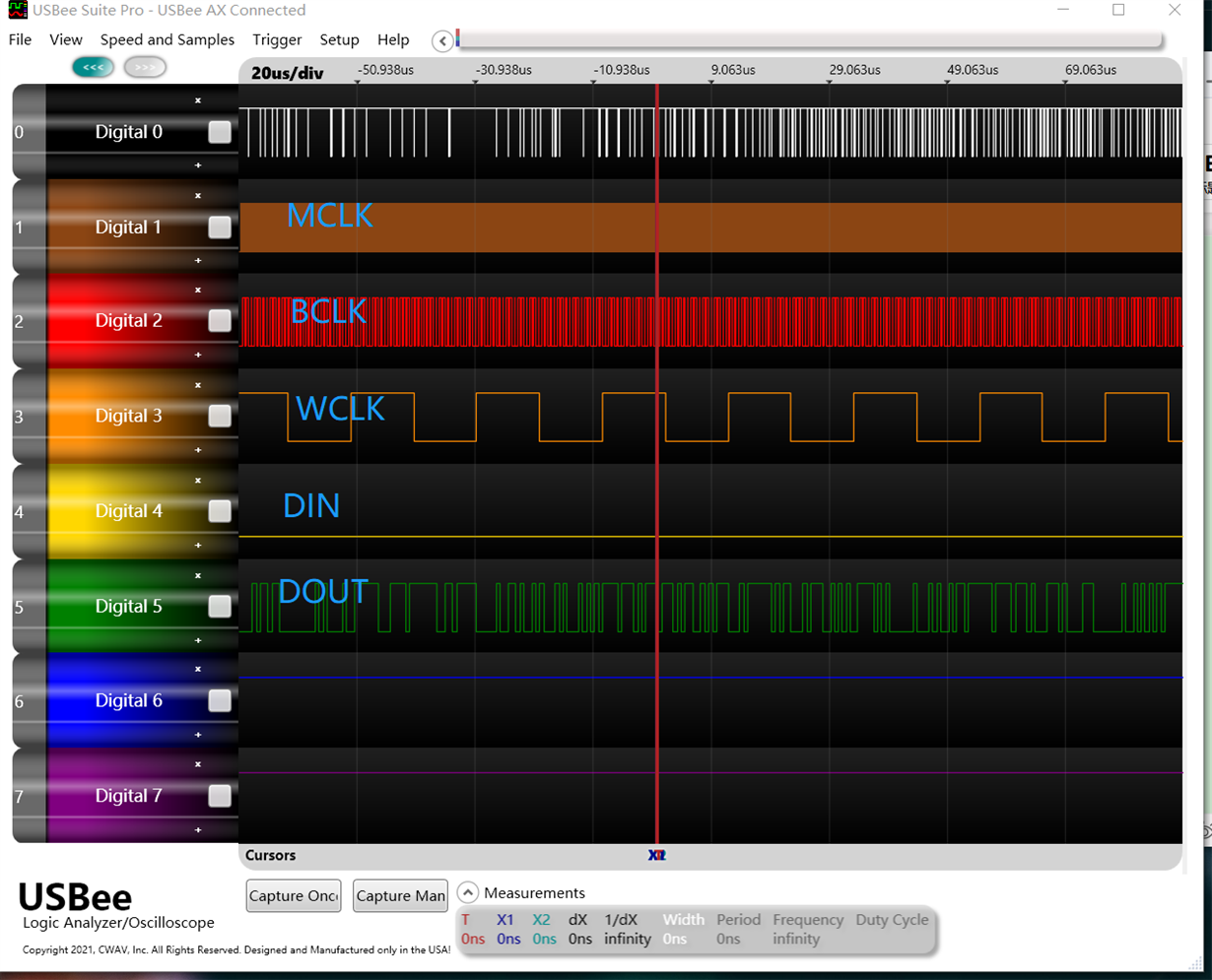

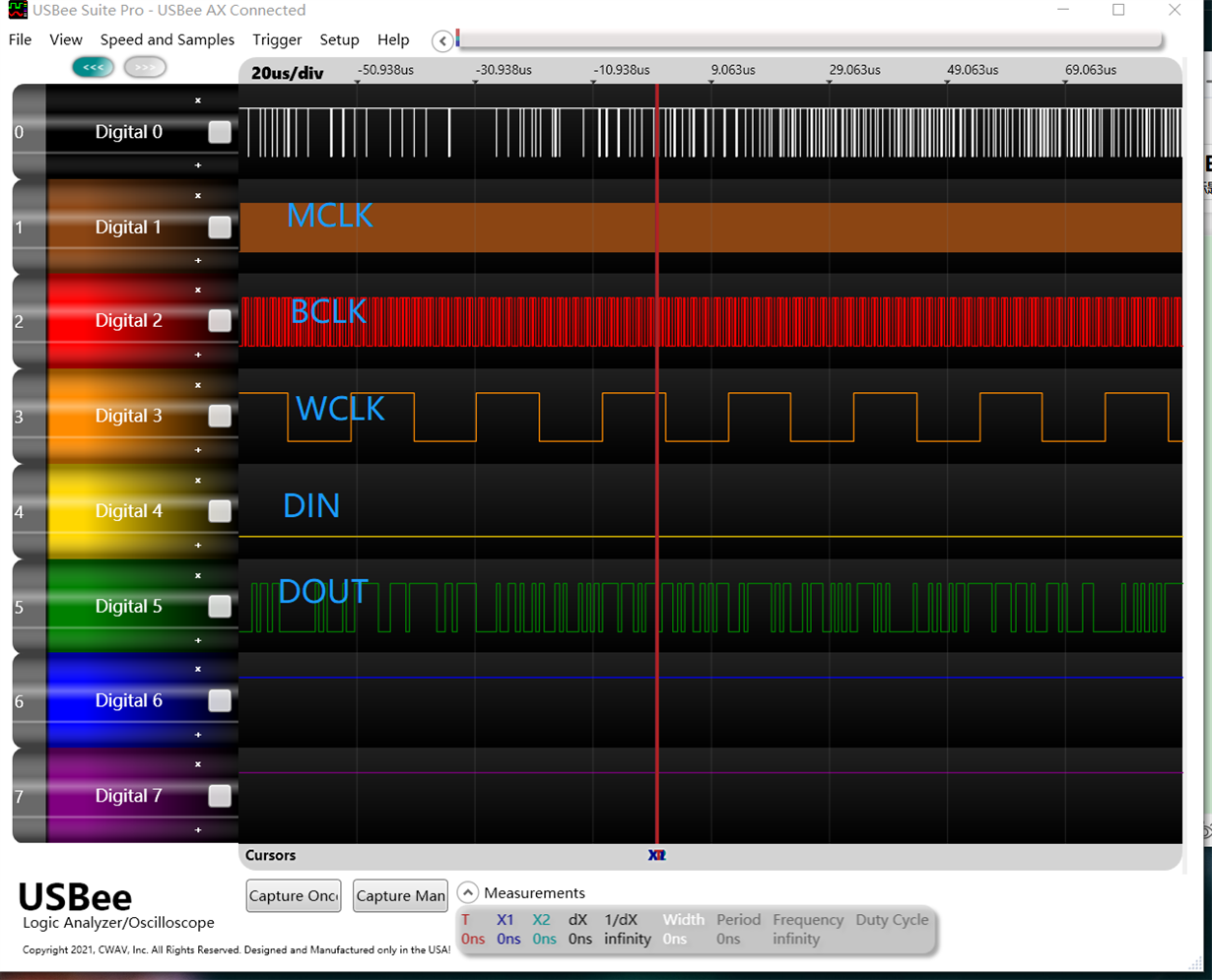

现象 使用STM32F104RE 做master tlv320aic3104 做slave ,参照datasheet配置完成后,再没有输入接入或者输入接地的情况下,I2S DOUT上有大量数据产生,正常输入波形信号也不能改变

问题1:

Master与slaver的 I2S 硬件直连,未加电容电阻,是否会有影响

问题2:

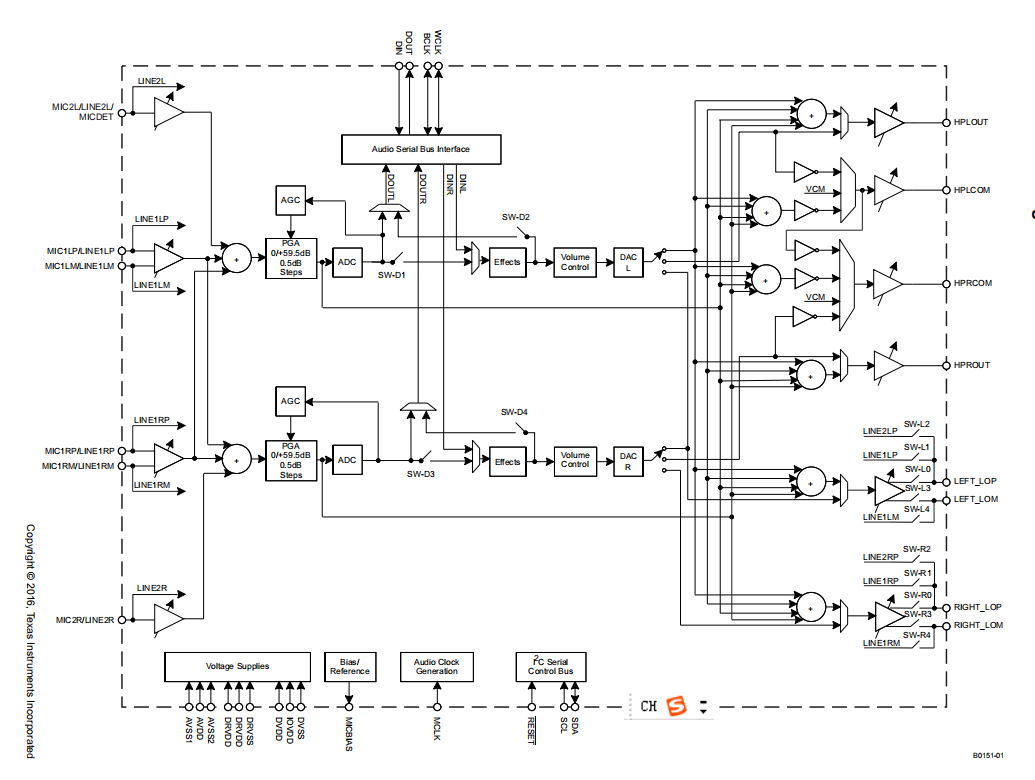

出现这种问题的可能原因,是否ADC或者I2S配置有问题?

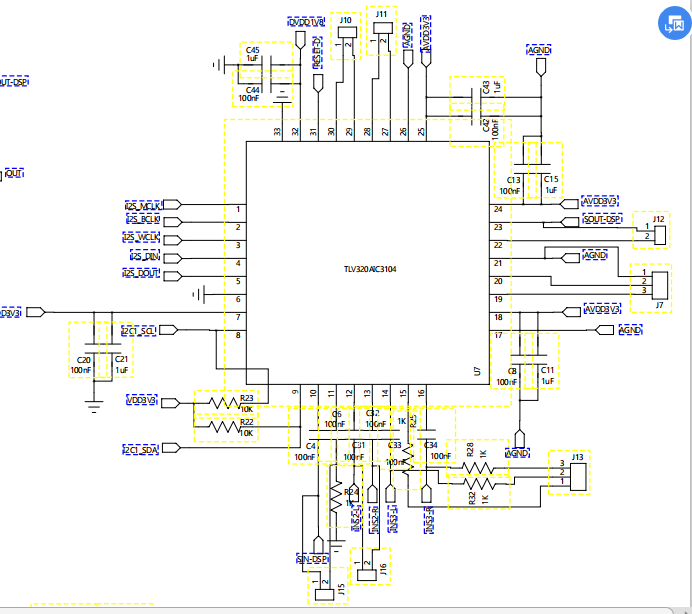

电路图如下:

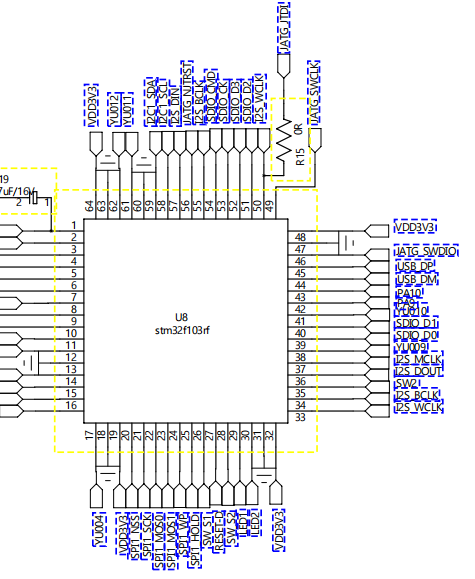

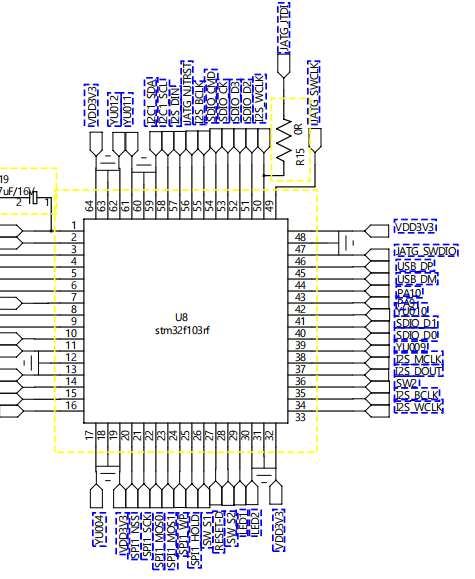

Master:

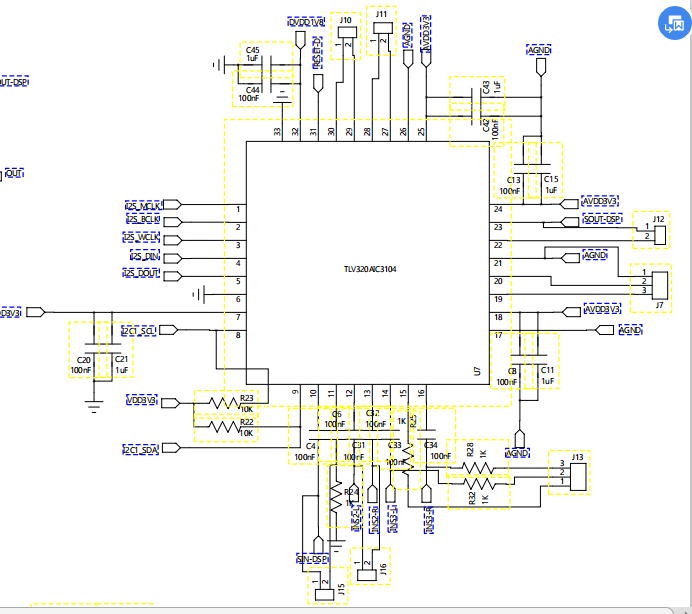

Slaver:

软件配置如下:

//CLOCK

{0, 0x00},

{1, 0x80},

{102, 0x02},

{101, 0x00}, //PLLDIV OUT

{7, 0x0A},

{2, 0x00}, //NEED CHECK

{3, 0x81}, //P = 1, R = 1, K = 8.192, which results in J = 8, D = 1920

{8, 0x20}, //BCLK/WCLK is input

{4, 0x20},

{5, 0x1E},

{6, 0x00},

//I2S

{8, 0x20}, //BCLK/WCLK is input

{9, 0x07}, //I2S mode, 16bit //Check if re-sync need.

{10, 0x00},//OFFSET = 0

//output

{14, 0x00},// 鐢靛杈撳嚭

{40, 0xB0}, //1.8V

{42, 0x8E}, // 杈撳嚭绾т笂鍗囧欢鏃?400ms锛屼俊鍙蜂笂鍗囨椂闂?4ms}

//ADC

{19, 0x04}, // MIC1LP CONNECT TO LEFT-ADC, LEFT-ADC is powered up.

{24, 0x00}, // MIC1LP CONNECT TO RIGHT-ADC471

{22, 0x7C}, // RIGHT-ADC power up

{25, 0x40}, // MICBIAS power down //need check

{15, 0x28}, //Unmute Left PGA, set gain to 26 dB

{16, 0xFF}, //Unmute RIGHT PGA, set gain to 26 dB

//DAC

{37, 0xE0}, // Left DAC and RIGHT DAC is powered up. HPLCOM configured as independent single-ended output

{41, 0x01}, //LEFT volume follows RIGHT

{43, 0x09},

{44, 0x09},

{38, 0x10}, // HPRCOM configured as independent single-ended output

{51, 0x89},

{47, 0x89},

{58, 0x00},

{54, 0x80},

{65, 0x89},

{64, 0x80},

{72, 0x00},

{71, 0x80},

{7, 0x0A},

逻辑分析仪截图如下

问题原文附件如下:tiv320aic3104 咨询.doc