Other Parts Discussed in Thread: TAS5733L

我使用了TAS5733L芯片想要做一个I2S放大的功放,设计目前出现的问题是,将ADR/FALUT设置为输出后,我在该引脚处加入了一个LED观察输出的是1还是0,结果是接上电源后,这个LED一闪一闪,也就是说ADR/FAULT引脚在高电平和低电平之间一直转换,请问这是哪个环节出了问题,根据数据手册取消了静音设置了主音量和左右声道音量接上喇叭并没有声音

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Other Parts Discussed in Thread: TAS5733L

我使用了TAS5733L芯片想要做一个I2S放大的功放,设计目前出现的问题是,将ADR/FALUT设置为输出后,我在该引脚处加入了一个LED观察输出的是1还是0,结果是接上电源后,这个LED一闪一闪,也就是说ADR/FAULT引脚在高电平和低电平之间一直转换,请问这是哪个环节出了问题,根据数据手册取消了静音设置了主音量和左右声道音量接上喇叭并没有声音

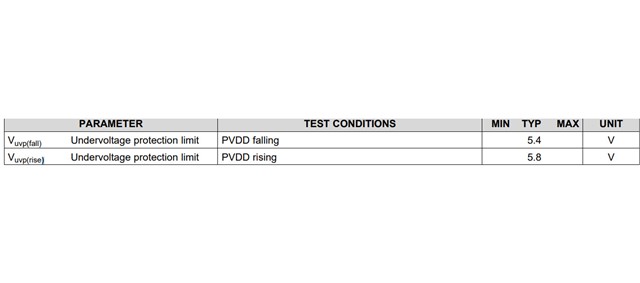

过压和欠压指的是AVDD和PVDD. datasheet中有描述,可以看大当PVDD和AVDD分别达到7.6V和2.7V时,才视为正常电压.

While powering up, the POR circuit resets the overload circuit (OLP) and ensures that all circuits are fully operational when the PVDD and AVDD supply voltages reach 7.6 V and 2.7 V.

PVDD的欠压有给出: