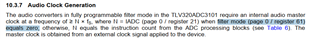

TLV320ADC3101 fs 跟mclk频率是什么关系,

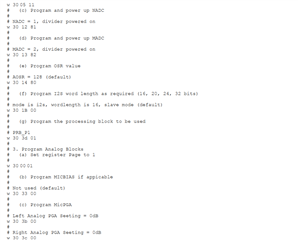

这里描述的 filter mode 是什么东西,怎样配置才是filter mode =0

when filter mode (page 0 / register 61)

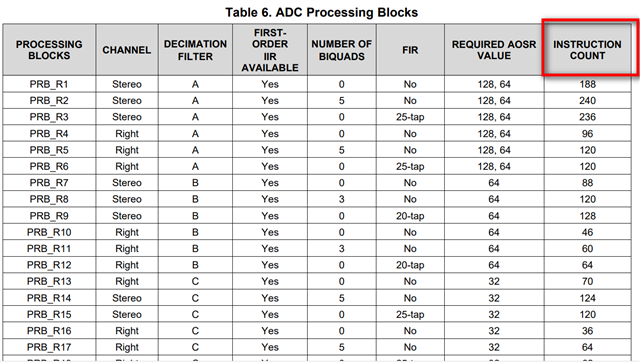

equals zero; otherwise, N equals the instruction count from the ADC processing blocks (see Table 6). The

master clock is obtained from an external clock signal applied to the device.