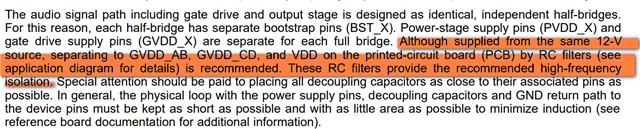

为了做一些TPA3255的实机测试,将官方开发板电路如下图所示简化后,做了一个小的测试模块(双层板,60mm x 70mm左右大小)。元器件选型及PCB布局布线基本都按照开发板来做。

测试时(PBTL模式,未带负载)使用keysight的台式电源E36234A向模块提供48V及12V的电源(双通道输出,输出电流最大值均限制为1A)。

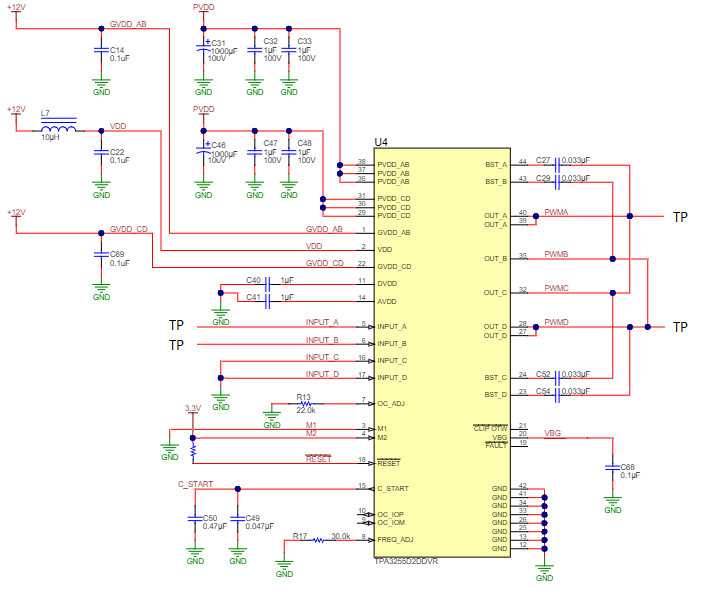

观测到在TPA3255输出的上升沿或下降沿处,GVDD/VDD引脚处波形会有一个幅值约1V的振荡(如图2所示,蓝线:GVDD波形,黄线:A通道PWM输出)。

直接测量台式电源输出端子的电压波形时,振荡明显减小(100-200mV左右)。

调整过台式电源至电路板间的供电线路的长度及电源入口处的电容容量,未发现有明显的改善。

以同样的供电方式给官方开发板供电时,未观测到这样的振荡。

想咨询一下,出现这样的振荡可能是什么地方出了问题,或者说还有什么地方可以做进一步调查确认。

麻烦了,谢谢。

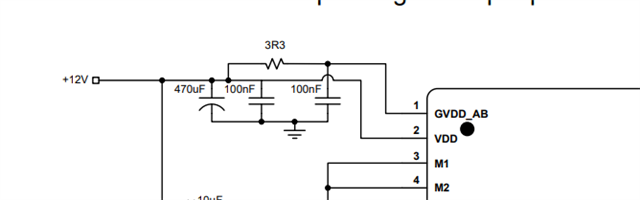

图1

图2