This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

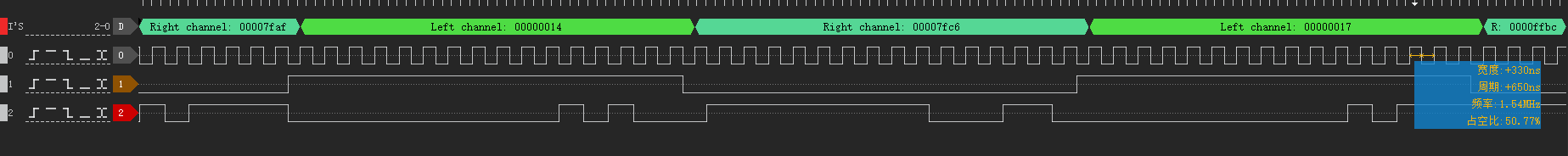

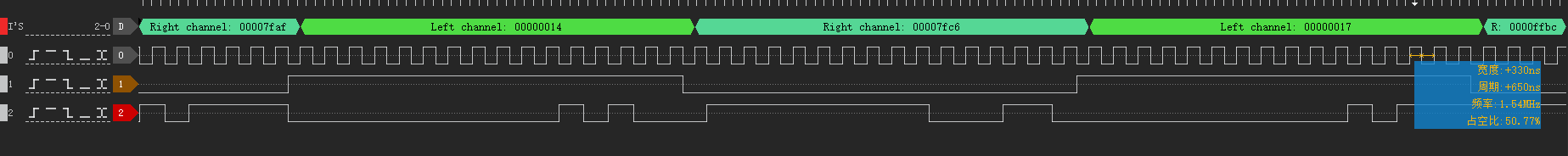

您好,出现TDM error就会导致进入software shutdown状态。

需要注意器件在退出shutdown模式之前时钟信号需要一直存在的。

您好。时钟信号一直存在的。

我们在每次调试也都会softreset一次,接着重新配置所有涉及到的寄存器。

您好,您参考下面这个帖子,和您的问题类似:

如还不能解决您的问题,再联系。

您好。TDM clock error现在正想办法解决。不过更令我们苦恼的是在INT_LTCH0中读出了Interrupt due to over current error。

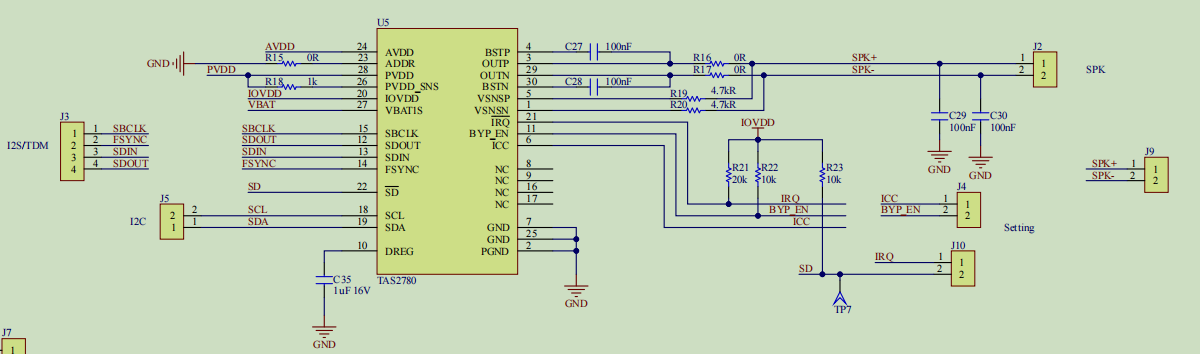

我们猜想或许是我们的电路设计有问题,以下是TAS2780的外围电路原理图,如果可以的话,请您帮我们进行斧正,感谢。

您好,将输出端电容C29 和C30去掉再试试,是否还报关于过流保护的错误?

您好,去掉输出端电容C29 和C30之后依旧会有 Interrupt due to over current error 的产生

您好,我又看了下您的电路,基本上没什么问题。

唯一一个和数据手册中不太符合的是,VSNSP和VSNSN的连接,如果C29和C30 没有去掉的话,VSNSP和VSNSN需要接在C29,C30的后面,也就是负载前面, 而不是C29和C30的前面。其他电路没看出问题来。

要么您换一块新的IC再试试。