你好:

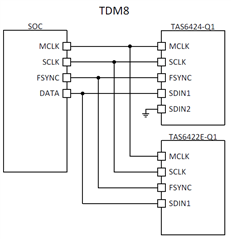

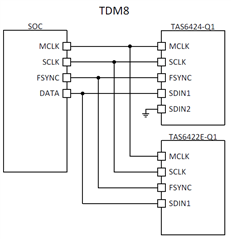

系统设计选择TAS6424E+TAS6422E 的AMP方案,硬件设计TDM接口的时候,为了节省DSP的接口数量,希望在下面电路上修改为把MCLK与SCLK 接到一起,这样使用有哪些限制?是否有其他问题?感谢支持

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

你好:

系统设计选择TAS6424E+TAS6422E 的AMP方案,硬件设计TDM接口的时候,为了节省DSP的接口数量,希望在下面电路上修改为把MCLK与SCLK 接到一起,这样使用有哪些限制?是否有其他问题?感谢支持

我翻看了TI E2E中文论坛和英文论坛有关 TAS6424E和TAS6422E的帖子,仅在下面帖子看到一个TIer专门发帖强调:将 FSYNC 占空比设置为>2BCLK,以确保在发生接地抖动的较差印刷电路板布局时不会出现 CLK 检测错误(for TDM8 audio format or application scenario which tied MCLK together with SCLK, it is proposed to set FSYNC duty cycle >2BCLK to make sure no CLK detection error when there is worse PCB layout with grounding jitter happening.)

关于这种配置是否有其他客户量产,很抱歉这个我们不清楚,因为这不属于我们要掌握的信息