想使用DRV595作为TEC的驱动芯片,有几个问题请教

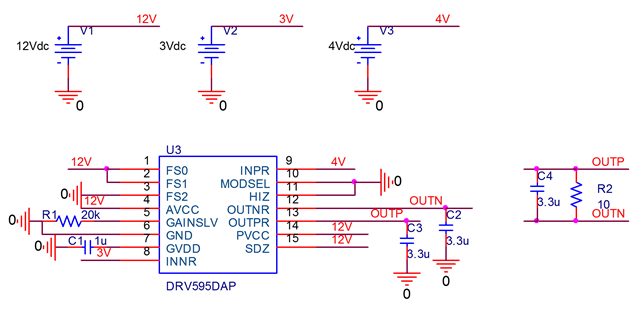

总体用法:如果单端输入,IN-接3V恒压,IN+在3V上下波动,OUTP和OUTN根据IN+和IN-的差值输出不同占空比的波形。PWM指的就是OUTP和OUTN输出波形

。不知道这么理解对不对?

有以下几个疑问:

1. 如果IN-接3V恒压,IN+的范围是多少呢?或者说当IN+大于多少时,OUTP一直为高电平,OUTN一直为低电平?这个时候Load current会一直增加吗?

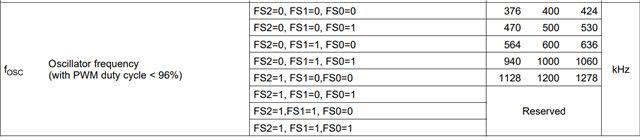

2. 手册中figure6~9中的frequency是什么频率?是OUTP和OUTN的PWM频率吗?表格ELECTRICAL CHARACTERISTICS中的fOSC(376kHz~1278kHz)又是什么?

3. GVDD=6.9V, 手册中"In Master mode, the SYNC terminal is an output, in Slave mode, the SYNC terminal is an input for a clock input.

TTL logic levels with compliance to GVDD." SYNC服从TTL电平标准,如何兼容GVDD呢?

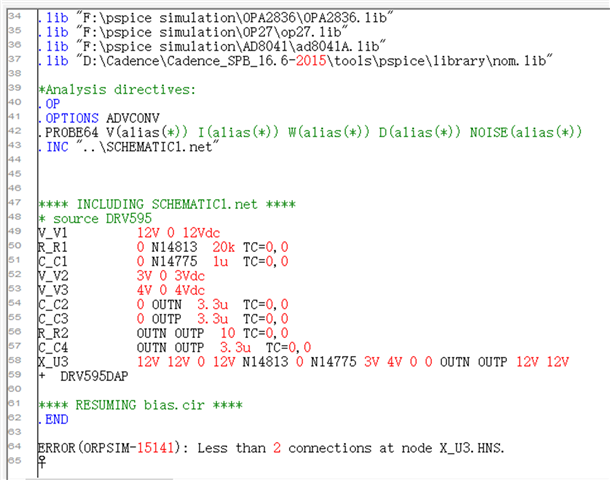

4. 我用网站的提供的Spice Model进行仿真,原理图如下,报错“Less than 2 connections at node X_U3.HNS.” 原理图封装没有HNS呀?

非常感谢!