麦克风从MIC2R输入,内部连接到左右声道,经过PGA 0db 放大后 音频直接输出到HPROUT端口监听,同时音频经过ADC输出数字信号。

另一端接收到ADC数据后还原后播放。 从HPROUT直接监听的音频没有底噪,经过ADC采样后的音频存在很大的底噪声。如果将PGA power down后,ADC的底噪消失。如果直接断开所有的音频输入端,只启动内部PGA 和 ADC 底噪仍然存在。

相关寄存器配置如下:

_WrData(0,0x00);

_WrData(1,0x80);//reset

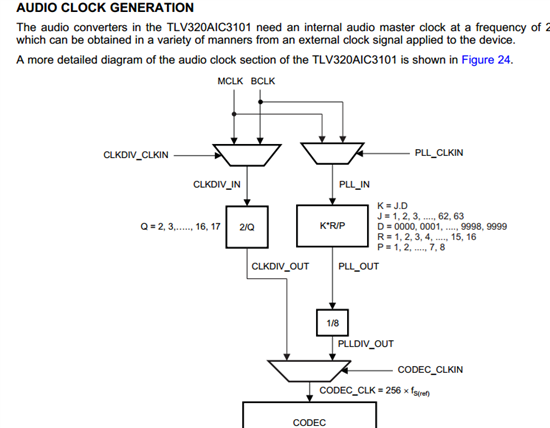

_WrData(3,0x10);//PLL is disabled, Q = 2.

_WrData(101,0x01);//clock use clkDIV_out

_WrData(102,0x02);//use MCLK

_WrData(7,0x8A);//AGC time constant fs=44.1Khz, left-DAC play left-channel input data, right-DAC play right-channel.

_WrData(9,0);//I2S mode. 16bit

_WrData(25,0x80);//MICBIAS 2.5V

_WrData(19,0x7C);//power up left ADC

_WrData(26,0x80);//enable left AGC

_WrData(17,0xf0);//MIC2R connect to left ADC

_WrData(15,0x0a);//left ADC PGA not mute,5db(0~59.5db)(增益可调)(x1111111)

_WrData(27,0x14);//left AGC gain 5db(0~59.5db)(可调)(与ADC增益一致)(1111111x)

_WrData(22,0x7c);//power up right ADC

_WrData(29,0x80);//enable right AGC

_WrData(18,0xf0);//MIC2R connect to right ADC

_WrData(16,0x0a);//left ADC PGA not mute,5db(0~59.5db)(增益可调)(x1111111)

_WrData(30,0x14);//left AGC gain 5db(0~59.5db)(可调)(与ADC增益一致)(1111111x)

_WrData(37,0x20);//power down left/right DAC, HPLCOM as single-end

_WrData(107,0x08);//ADC digital output to programmable filter path

_WrData(65,0x0d);//HPROUT level 0db(0~9db), unmute HPROUT,HPROUT power up

_WrData(63,0x80);//PGA_R to HPROUT, 0db(0db~-78.3db)(可调)