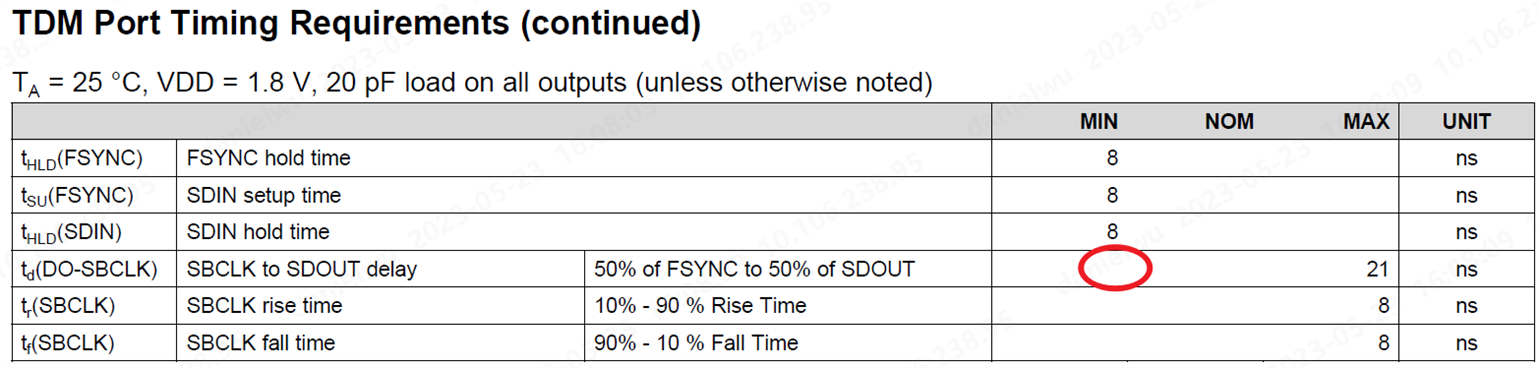

当SBCLK=24.576Mhz时,时钟周期是40.69ns。

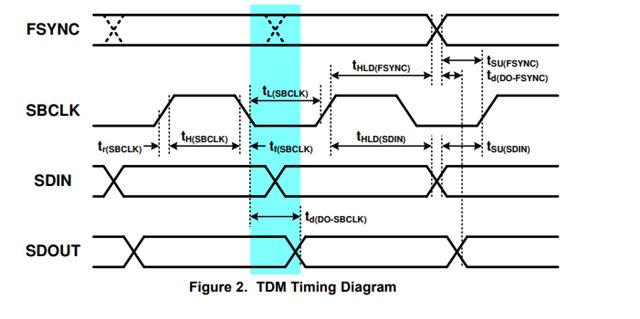

td(DO-SBCLK)是SBCLK下降沿到SDOUT发出的delay。

当td(DO-SBCLK)=21ns时,Master端的 setup time = 40.69/2-21=-0.655ns 已经完全不能实现了。

是我理解有问题,还是怎么回事,请帮忙解释一下。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

很抱歉回复这么晚!美国工程师的回复:

The timing provided for the SBCLK to SDOUT delay is from one sample to the other, ie. if the data is sampled on the falling edge of SBCLK, the delay time is from the last SBCLK falling edge to the next sample of SDOUT, meaning you actually have 40ns - 21ns = 19ns to setup the next SDOUT sample.

If data is sampled on rising edge, you would consider the same but from SBCLK rising edge perspective, as opposed to consider the next opposite edge of SBCLK.

Regarding capacitive load, the timing diagrams already consider the capacitive load as specified at the top of the table.

Hopefully this helps to clarify the timing requirements.

首先请注意这个时间是sample to sample 之间的,不是bit to bit 之间的,注意看时序图最上方的FSYNC(TDM frame sync)信号

您是在上升沿采样数据吗?

If data is sampled on rising edge, you would consider the same but from SBCLK rising edge perspective, as opposed to consider the next opposite edge of SBCLK.

那么意思就是说这个 SBCLK to SDOUT delay是从SBCLK 上升沿到下一个sample的SDOUT的延迟。注意红色字体都是上升沿。

你仔细理解下这句话:If data is sampled on rising edge, you would consider the same but from SBCLK rising edge perspective, as opposed to consider the next opposite edge of SBCLK.

然后您描述说“Master是SBCLK上升沿前tsu(SDIN)”,那么您的意思不是在上升沿采样数据吗?根据上面这句话,如果是在上升沿采样就需要看SBCLK的上升沿,或者说以SBCLK的上升沿为标准看延迟

”如果是在上升沿采样就需要看SBCLK的上升沿,或者说以SBCLK的上升沿为标准看延迟“,这句话的意思是说td(DO-SBCLK)也可以以SBCLK的上升沿为起点,而不是timing图上标示的下降沿,对么?

基于上述观点正确,我还有几个疑问:

1. td(DO-SBCLK)的起点什么时候基于SBCLK上升沿,什么时候基于SBCLK下降沿;

2. 默认是使用上升沿还是下降沿?是如何切换的?

3. td(DO-SBCLK)的最小值是多少?基于上升沿情况下 td(DO-SBCLK)取最小值,这个时候Master的hold time是否能满足又是一个风险问题了。

主控端只能在SBCLK的上升沿读取数据。这个跟主控端的设置关系不大,还是取决于 td(DO-SBCLK)的最小值和最大值的区间范围,能否同时适配Slave 发出 DOUT在SBCLK上升沿或下降沿。

具体来说,当td(DO-SBCLK)取最大值21ns时,Slave 发出 DOUT就只能在SBCLK的上升沿;如果 下一批次的td(DO-SBCLK)取最小值,软件沿用DOUT在SBCLK的上升沿发出,这个时候就要看看这个td(DO-SBCLK)取最小值是否能满足Master的hold time了。

还是取决于 td(DO-SBCLK)的最小值和最大值的区间范围,能否同时适配Slave 发出 DOUT在SBCLK上升沿或下降沿。

是的,能否同时适配在SBCLK上升沿或下降沿发出DOUT,取决于td(DO-SBCLK)的具体值,如果延迟为1/4周期SBCLK,那么这是适配SBCLK上升沿或下降沿发出DOUT的最好条件。

具体来说,当td(DO-SBCLK)取最大值21ns时,Slave 发出 DOUT就只能在SBCLK的上升沿;

是的,延迟21ns相当于1/2周期SBCLK,如果主控端是上升沿读取数据,那么需要设置DOUT在上升沿发出。

如果 下一批次的td(DO-SBCLK)取最小值,软件沿用DOUT在SBCLK的上升沿发出,这个时候就要看看这个td(DO-SBCLK)取最小值是否能满足Master的hold time了。

是的,同时也与PCB layout走线长度也有关系,PCB走线也会带来传输延迟。

主控端只能在SBCLK的上升沿读取数据。这个跟主控端的设置关系不大,还是取决于 td(DO-SBCLK)的最小值和最大值的区间范围,能否同时适配Slave 发出 DOUT在SBCLK上升沿或下降沿。

具体来说,当td(DO-SBCLK)取最大值21ns时,Slave 发出 DOUT就只能在SBCLK的上升沿;如果 下一批次的td(DO-SBCLK)取最小值,软件沿用DOUT在SBCLK的上升沿发出,这个时候就要看看这个td(DO-SBCLK)取最小值是否能满足Master的hold time了

您可以给出您担忧情况的示意图吗?以方便我向美国的工程师描述清楚您的问题。

您误解了我的意思:

我已经在向美国的工程师确认了,

我的意思是我已经找对应工程师来提供这个值了,但是这个工程师他可能认为不需要td的最小值,所以一直在问是在什么情况下需要这个最小值;

或者说他认为没必要提供此值,所以一直不提供此值。

现在我需要您一个理由让他去找或提供此值。

您的意思是说:

主控端只能在SBCLK的上升沿采样,而TAS2564 可以设置在SBCLK下降沿或上升沿发出数据。

当设置 TAS2564在下降沿发出数据时,如果所使用的TAS2564 的td(DO-SBCLK)值是21ns时,就不能有6ns的setup时间.

或 当设置 TAS2564在上降沿发出数据时,如果所使用的TAS2564 的td(DO-SBCLK)值是0ns时,就不能有4ns的hold 时间.

我上述是否正确描述了您的担忧?

我不太明白BCLK和BCLK_inv 是什么波形?当设置TAS2564在上降沿发出数据时,BCLK_inv为什么与BCLK_SOC反向?

得到的回复:

Hope this helps close this question, let us know otherwise.