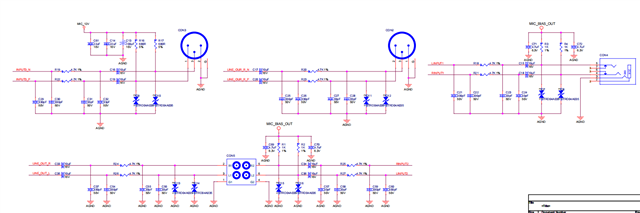

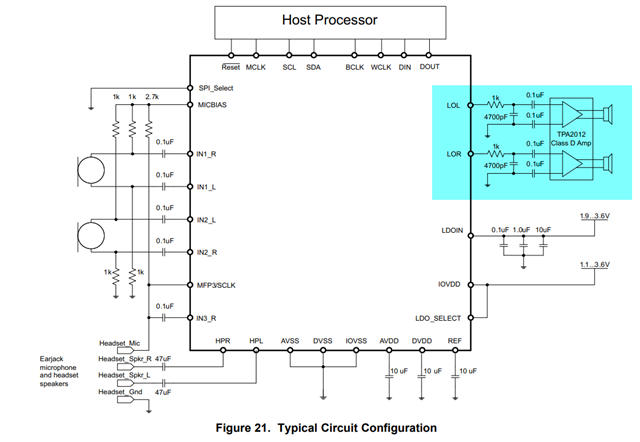

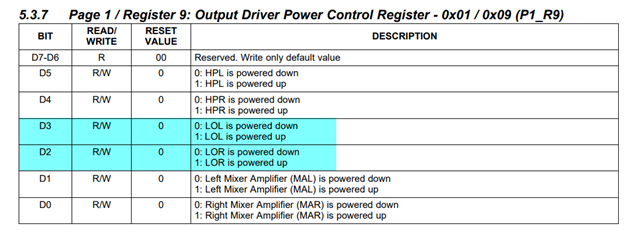

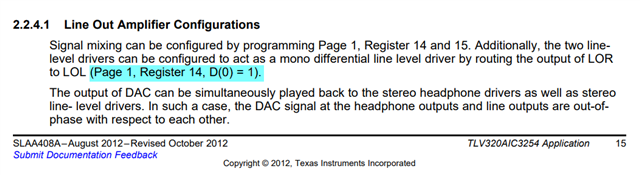

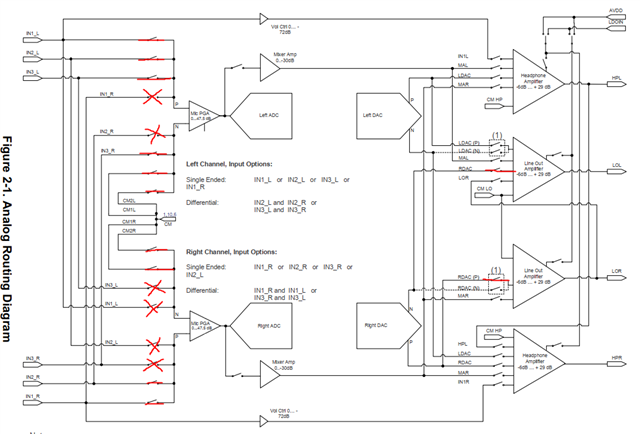

硬件设计DAC是Line out差分输出,代码及路由图如下,但测试到RightDAC N,P对应的rdac_lol,rdac_lor = 1输出的信号是相同,并不是差分反相。这个问题出在哪里?

/**************** INOUT CONFIG ***********/

//reg page1, 0x34

audio_ctrl.micpga_left.in1l_micpga = AIC32x4_ROUTED_WITH_10K_RES;

audio_ctrl.micpga_left.in2l_micpga = AIC32x4_ROUTED_WITH_10K_RES;

audio_ctrl.micpga_left.in3l_micpga = AIC32x4_ROUTED_WITH_10K_RES;

audio_ctrl.micpga_left.in1r_micpga = AIC32x4_NOT_ROUTED;

ioctl(s_fdTlv,MICPGA_LEFT_POSITIVE_INPUT , &audio_ctrl);

//reg page1, 0x36

audio_ctrl.micpga_left.in2r_micpga = AIC32x4_NOT_ROUTED;

audio_ctrl.micpga_left.in3r_micpga = AIC32x4_ROUTED_WITH_10K_RES;

audio_ctrl.micpga_left.cm_micpga_via_cm1l = AIC32x4_ROUTED_WITH_10K_RES;

audio_ctrl.micpga_left.cm_micpga_via_cm2l = AIC32x4_ROUTED_WITH_10K_RES;

ioctl(s_fdTlv,MICPGA_LEFT_NEGTIVE_INPUT , &audio_ctrl);

//reg page1, 0x37

audio_ctrl.micpga_right.in1r_micpga = AIC32x4_ROUTED_WITH_10K_RES;

audio_ctrl.micpga_right.in2r_micpga = AIC32x4_ROUTED_WITH_10K_RES;

audio_ctrl.micpga_right.in3r_micpga = AIC32x4_NOT_ROUTED;

audio_ctrl.micpga_right.in2l_micpga = AIC32x4_NOT_ROUTED;

ioctl(s_fdTlv, MICPGA_RIGHT_POSITIVE_INPUT , &audio_ctrl);

//reg page1, 0x39

audio_ctrl.micpga_right.cm_micpga_via_cm1r = AIC32x4_ROUTED_WITH_10K_RES;

audio_ctrl.micpga_right.cm_micpga_via_cm2r = AIC32x4_ROUTED_WITH_10K_RES;

audio_ctrl.micpga_right.in3l_micpga = AIC32x4_NOT_ROUTED;

audio_ctrl.micpga_right.in1l_micpga = AIC32x4_NOT_ROUTED;

ioctl(s_fdTlv, MICPGA_RIGHT_NEGTIVE_INPUT , &audio_ctrl);

/************ LOL/R differential **************/

//LOL ROUTE

audio_ctrl.lo.rdac_lol = 1;

audio_ctrl.lo.ldac_lol = 0;

audio_ctrl.lo.mal_lol = 0;

audio_ctrl.lo.lor_lol = 0;

ioctl(s_fdTlv, LOL_INPUT, &audio_ctrl);

//LOR ROUTE

audio_ctrl.lo.rdac_lor = 1;

audio_ctrl.lo.mar_lor = 0;

ioctl(s_fdTlv, LOR_INPUT, &audio_ctrl);

/************ HPL/R SINGLE ENDED **************/

audio_ctrl.hp.ldac_hpl = 1;

audio_ctrl.hp.in1l_hpl = 0;

audio_ctrl.hp.mal_hpl = 0;

audio_ctrl.hp.mar_hpl = 0;

ioctl(s_fdTlv, HPL_INPUT, &audio_ctrl);

audio_ctrl.hp.ldac_hpr = 0;

audio_ctrl.hp.rdac_hpr = 1;

audio_ctrl.hp.in1r_hpr = 0;

audio_ctrl.hp.mar_hpr = 0;

audio_ctrl.hp.hpl_hpr = 0;

ioctl(s_fdTlv, HPR_INPUT, &audio_ctrl);

/******* HPL/R POWER **************/

audio_ctrl.powerup.hpl_power_up = AIC32x4_ENABLE;

ioctl(s_fdTlv, HEADPHONE_LEFT_POWER_UP, &audio_ctrl);

audio_ctrl.powerup.hpr_power_up = AIC32x4_ENABLE;

ioctl(s_fdTlv, HEADPHONE_RIGHT_POWER_UP, &audio_ctrl);

audio_ctrl.powerup.lol_power_up = AIC32x4_ENABLE;

ioctl(s_fdTlv,LINE_OUT_LEFT_POWER_UP , &audio_ctrl);

audio_ctrl.powerup.lor_power_up = AIC32x4_ENABLE;

ioctl(s_fdTlv,LINE_OUT_RIGHT_POWER_UP , &audio_ctrl);