Some question about data sheet of Tas5722L

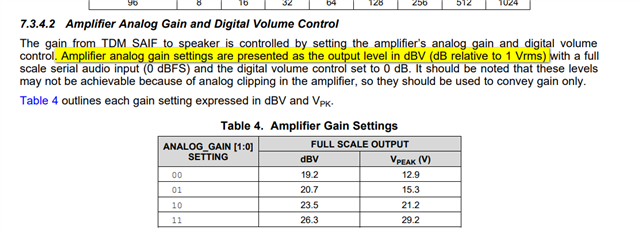

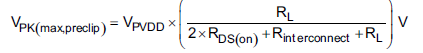

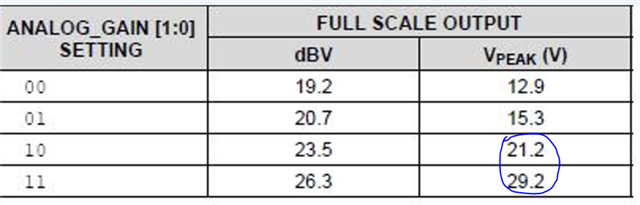

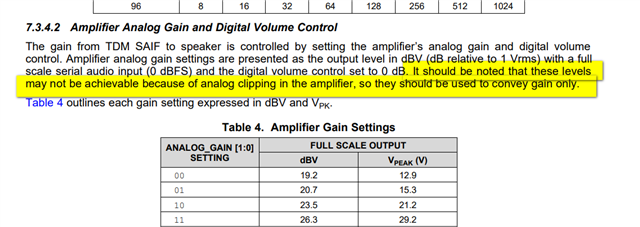

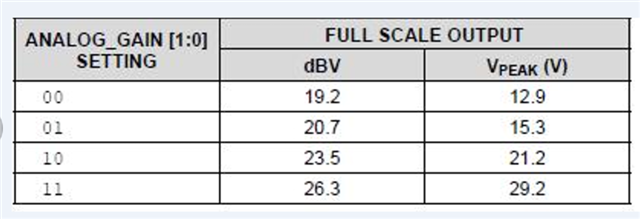

- For this part of TAS5722L datasheet,how to calculate dBV from Vpeak? I tried dBV=20log10(Vpeak),

which gives unmatched results with the following chart

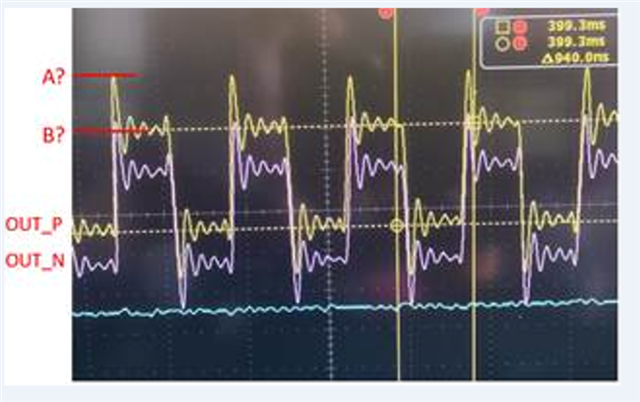

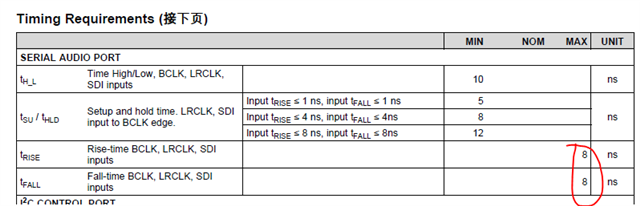

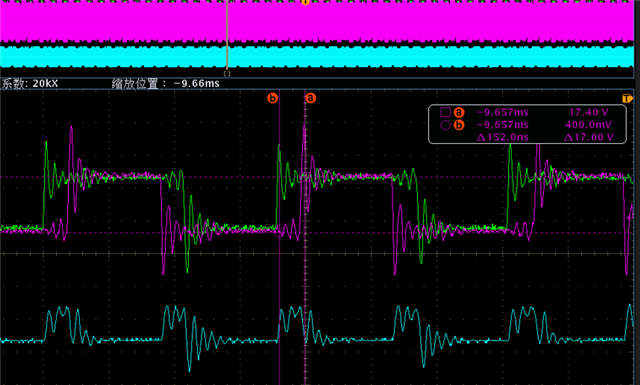

2.By the way, How to measure Vpaek with oscilloscope, e.g., A or B?