Part Number: TLV320AIC3104

Other Parts Discussed in Thread: REG101,

1:通路配置需要修改那些寄存器,目前我们是一路tdm进来,输出接的是LEFT_LOP、RIGHT_LOP和HPLOUT三路,我们tlv320aic31x.c驱动里注了很多snd_kcontrol,这些是否能利用起来,麻烦提供一些相关的测试示例。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: TLV320AIC3104

Other Parts Discussed in Thread: REG101,

1:通路配置需要修改那些寄存器,目前我们是一路tdm进来,输出接的是LEFT_LOP、RIGHT_LOP和HPLOUT三路,我们tlv320aic31x.c驱动里注了很多snd_kcontrol,这些是否能利用起来,麻烦提供一些相关的测试示例。

git.kernel.org/.../tlv320aic3x.c

aic3x_regread >>> REG: 2, DATA = 0x00.

aic3x_regread >>> REG: 3, DATA = 0x91.

aic3x_regread >>> REG: 4, DATA = 0x80.

aic3x_regread >>> REG: 5, DATA = 0x00.

aic3x_regread >>> REG: 6, DATA = 0x00.

aic3x_regread >>> REG: 7, DATA = 0x0a.

aic3x_regread >>> REG: 8, DATA = 0x00.

aic3x_regread >>> REG: 9, DATA = 0x00.

aic3x_regread >>> REG: 10, DATA = 0x00.

aic3x_regread >>> REG: 11, DATA = 0x02.

aic3x_regread >>> REG: 12, DATA = 0x00.

aic3x_regread >>> REG: 13, DATA = 0x00.

aic3x_regread >>> REG: 14, DATA = 0x00.

aic3x_regread >>> REG: 15, DATA = 0x20.

aic3x_regread >>> REG: 16, DATA = 0x20.

aic3x_regread >>> REG: 17, DATA = 0xff.

aic3x_regread >>> REG: 18, DATA = 0xff.

aic3x_regread >>> REG: 19, DATA = 0x00.

aic3x_regread >>> REG: 20, DATA = 0x78.

aic3x_regread >>> REG: 21, DATA = 0x78.

aic3x_regread >>> REG: 22, DATA = 0x00.

aic3x_regread >>> REG: 23, DATA = 0x78.

aic3x_regread >>> REG: 24, DATA = 0x78.

aic3x_regread >>> REG: 25, DATA = 0x00.

aic3x_regread >>> REG: 26, DATA = 0x00.

aic3x_regread >>> REG: 27, DATA = 0xfe.

aic3x_regread >>> REG: 28, DATA = 0x00.

aic3x_regread >>> REG: 29, DATA = 0x00.

aic3x_regread >>> REG: 30, DATA = 0xfe.

aic3x_regread >>> REG: 31, DATA = 0x00.

aic3x_regread >>> REG: 32, DATA = 0x18.

aic3x_regread >>> REG: 33, DATA = 0x18.

aic3x_regread >>> REG: 34, DATA = 0x00.

aic3x_regread >>> REG: 35, DATA = 0x00.

aic3x_regread >>> REG: 36, DATA = 0x00.

aic3x_regread >>> REG: 37, DATA = 0x00.

aic3x_regread >>> REG: 38, DATA = 0x00.

aic3x_regread >>> REG: 39, DATA = 0x00.

aic3x_regread >>> REG: 40, DATA = 0x80.

aic3x_regread >>> REG: 41, DATA = 0x00.

aic3x_regread >>> REG: 42, DATA = 0x00.

aic3x_regread >>> REG: 43, DATA = 0xaf.

aic3x_regread >>> REG: 44, DATA = 0xaf.

aic3x_regread >>> REG: 45, DATA = 0x00.

aic3x_regread >>> REG: 46, DATA = 0x2f.

aic3x_regread >>> REG: 47, DATA = 0xaf.

aic3x_regread >>> REG: 48, DATA = 0x00.

aic3x_regread >>> REG: 49, DATA = 0x00.

aic3x_regread >>> REG: 50, DATA = 0x00.

aic3x_regread >>> REG: 51, DATA = 0x0c.

aic3x_regread >>> REG: 52, DATA = 0x00.

aic3x_regread >>> REG: 53, DATA = 0x2f.

aic3x_regread >>> REG: 54, DATA = 0xaf.

aic3x_regread >>> REG: 55, DATA = 0x00.

aic3x_regread >>> REG: 56, DATA = 0x00.

aic3x_regread >>> REG: 57, DATA = 0x00.

aic3x_regread >>> REG: 58, DATA = 0x0c.

aic3x_regread >>> REG: 59, DATA = 0x00.

aic3x_regread >>> REG: 60, DATA = 0x00.

aic3x_regread >>> REG: 61, DATA = 0x00.

aic3x_regread >>> REG: 62, DATA = 0x00.

aic3x_regread >>> REG: 63, DATA = 0x2f.

aic3x_regread >>> REG: 64, DATA = 0xaf.

aic3x_regread >>> REG: 65, DATA = 0x0c.

aic3x_regread >>> REG: 66, DATA = 0x00.

aic3x_regread >>> REG: 67, DATA = 0x00.

aic3x_regread >>> REG: 68, DATA = 0x00.

aic3x_regread >>> REG: 69, DATA = 0x00.

aic3x_regread >>> REG: 70, DATA = 0x2f.

aic3x_regread >>> REG: 71, DATA = 0xaf.

aic3x_regread >>> REG: 72, DATA = 0x0c.

您好,

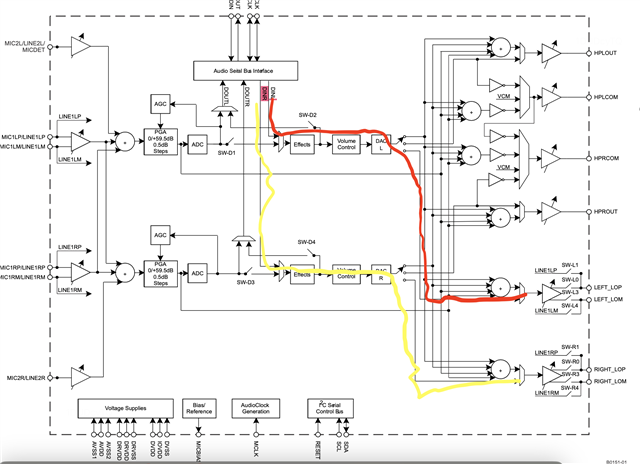

在 datasheet 21页 Figure 10-2. Functional Block Diagram With Registers,这个框图路径中带有寄存器,您可以对照着上面的寄存器配置。

另外,下面应用手册希望对您有帮助:

TLV320AIC3104 Programming Made Easy 第6部分有Example Code

Audio Serial Interface Configurations for Audio Codecs (Rev. A)

很抱歉,没有测试示例提供给您。

下面文档第5部分有 TDM mode 示例您看下是否有帮助:

按照以上寄存器配置完后,我这里播放音乐的时候,LEFT_LOP、RIGHT_LOP和HPLOUT全是高电平

寄存器如下:

2, DATA = 0x00.

3, DATA = 0x91.

4, DATA = 0x80.

5, DATA = 0x00.

6, DATA = 0x00.

7, DATA = 0x14.

8, DATA = 0x00.

9, DATA = 0x40.

10, DATA = 0x00.

11, DATA = 0x02.

12, DATA = 0x00.

13, DATA = 0x00.

14, DATA = 0x00.

15, DATA = 0x20.

16, DATA = 0x20.

17, DATA = 0xff.

18, DATA = 0xff.

19, DATA = 0x00.

20, DATA = 0x78.

21, DATA = 0x78.

22, DATA = 0x00.

23, DATA = 0x78.

24, DATA = 0x78.

25, DATA = 0x00.

26, DATA = 0x00.

27, DATA = 0xfe.

28, DATA = 0x00.

29, DATA = 0x00.

30, DATA = 0xfe.

31, DATA = 0x00.

32, DATA = 0x18.

33, DATA = 0x18.

34, DATA = 0x00.

35, DATA = 0x00.

36, DATA = 0x00.

37, DATA = 0xe0.

38, DATA = 0x00.

39, DATA = 0x00.

40, DATA = 0x80.

41, DATA = 0x02.

42, DATA = 0x00.

43, DATA = 0xaf.

44, DATA = 0xaf.

45, DATA = 0x00.

46, DATA = 0x2f.

47, DATA = 0xaf.

48, DATA = 0x00.

49, DATA = 0x00.

50, DATA = 0x00.

51, DATA = 0x9d.

52, DATA = 0x00.

53, DATA = 0x2f.

54, DATA = 0xaf.

55, DATA = 0x00.

56, DATA = 0x00.

57, DATA = 0x00.

58, DATA = 0x9d.

59, DATA = 0x00.

60, DATA = 0x00.

61, DATA = 0x00.

62, DATA = 0x00.

63, DATA = 0x2f.

64, DATA = 0xaf.

65, DATA = 0x0f.

66, DATA = 0x00.

67, DATA = 0x00.

68, DATA = 0x00.

69, DATA = 0x00.

70, DATA = 0x2f.

71, DATA = 0xaf.

72, DATA = 0x0f.

73, DATA = 0x00.

74, DATA = 0x00.

75, DATA = 0x00.

76, DATA = 0x00.

77, DATA = 0x00.

78, DATA = 0x00.

79, DATA = 0x00.

80, DATA = 0x00.

81, DATA = 0x2f.

82, DATA = 0xf4.

83, DATA = 0x00.

84, DATA = 0xf4.

85, DATA = 0x00.

86, DATA = 0x09.

87, DATA = 0x00.

88, DATA = 0x00.

89, DATA = 0x00.

90, DATA = 0x00.

91, DATA = 0x2f.

92, DATA = 0xaf.

93, DATA = 0x09.

94, DATA = 0xc4.

95, DATA = 0x00.

96, DATA = 0x00.

97, DATA = 0x00.

98, DATA = 0x00.

99, DATA = 0x00.

100, DATA = 0x00.

101, DATA = 0x00.

102, DATA = 0xa2.

103, DATA = 0x00.

104, DATA = 0x00.

105, DATA = 0x00.

106, DATA = 0x00.

107, DATA = 0x00.

108, DATA = 0x00.

109, DATA = 0x40.

您好,按照要求,把43和44寄存器配置成0x7f,我们采用的是内部bclk时钟,频率为1.536MHZ,从模式,没有使用mclk,采样率是48khz,pll enable,p=1,r=2,J=32, D=0,采用的dsp模式(tdm),播放音乐有杂音,杂音很小,但是没有音乐输出,测量LEFT_LOP、RIGHT_LOP的电压一直是3.3v

reg 1 data 80

reg 3 data 91

reg 4 data 80

reg 5 data 00

reg 6 data 00

reg 7 data 1e

reg 8 data 00

reg 9 data 40

reg 11 data 02

reg 41 data 50

reg 43 data 7f

reg 44 data 7f

reg 37 data c0

reg 82 data ff

reg 85 data ff

reg 86 data 9b

reg 89 data ff

reg 92 data ff

reg 93 data 9b

reg 102 data e2

将 43和44寄存器配置成0x7f,增益太小了,建议先不要衰减。

我们采用的是内部bclk时钟,频率为1.536MHZ,

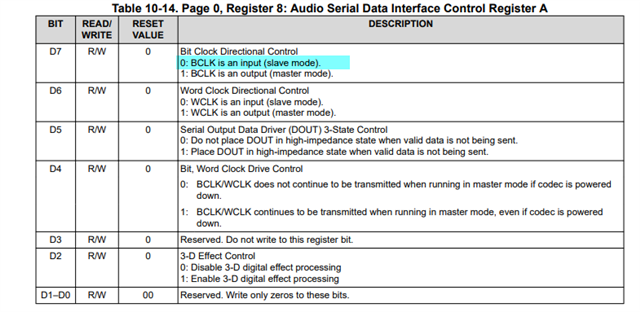

但是您寄存器8配置的是00,即BCLK is an input,reg 102 data e2 那么BCLK 时钟信号从哪里来的?

reg 82 data ff

reg 85 data ff

reg 89 data ff

reg 92 data ff

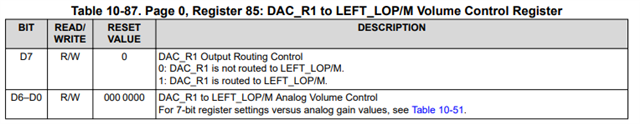

寄存器82、85 、89、92 音量配置全1也是mute,具体见datasheet Table 10-51.

您好,按照要求我们的把43和44寄存器配置成0x00,我们采用的是内部bclk时钟,频率为3.072MHZ,主模式,由soc输出wclk=48khz,bclk =3.072M, 没有使用mclk,采样率是48khz,pll enable,p=1,r=2,J=16, D=0,采用的dsp模式(tdm),播放音乐时候有杂音,杂音很大,有音乐输出,但是被杂音覆盖。reg 102 = a2的时候有以上的噪音,但是reg 102 = e2的时候没有声音输出。

reg 1 data 80

reg 3 data 91

reg 4 data 80

reg 5 data 00

reg 6 data 00

reg 7 data 1e

reg 8 data c0

reg 9 data 40

reg 11 data 02

reg 41 data 50

reg 43 data 00

reg 44 data 00

reg 37 data c0

reg 82 data e4

reg 85 data e4

reg 86 data 9b

reg 89 data e4

reg 92 data e4

reg 93 data 9b

reg 102 data e2

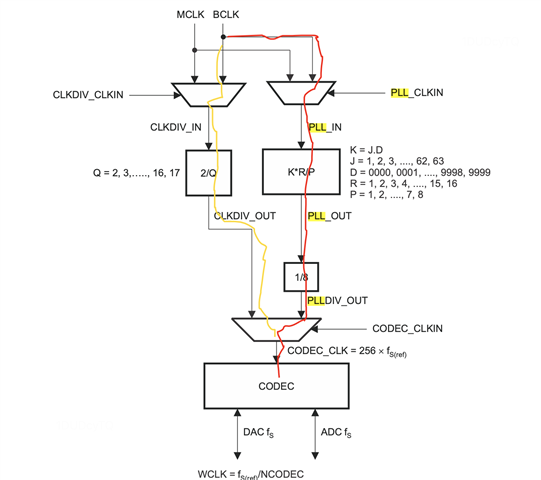

我希望走的是红色的时钟配置,但是我配置成红色的后,声音没有输出,但是黄色和红色都配置后,就会有上面的现象,并且reg101=0x00 ,还请麻烦check一下我的关于clk相关的寄存器配置

我们采用的是内部bclk时钟,频率为3.072MHZ,主模式,由soc输出wclk=48khz,bclk =3.072M, 没有使用mclk,

您这里指 TLV320AIC3104工作在主模式吗?因为看到您下面 reg 8 配置为 data c0,那么TLV320AIC3104工作在主模式时BCLK和WCLK都是从TLV320AIC3104 输出的,您这里又描述“由soc输出wclk=48khz,bclk =3.072M, 没有使用mclk”,因此我不明白您到底期望工作在什么模式下。如果工作在主模式下,BCLK和WCLK应该都是输出,如果工作在从模式下,BCLK和WCLK应该都是输入。

我们需要工作在从模式,BCLK和WCLK都是有高通的soc提供

reg 1 data 80

reg 3 data 91

reg 4 data 80

reg 5 data 00

reg 6 data 00

reg 7 data 1e

reg 8 data 00

reg 9 data 40

reg 11 data 02

reg 41 data 50

reg 43 data 00

reg 44 data 00

reg 37 data c0

reg 82 data e4

reg 85 data e4

reg 86 data 9b

reg 89 data e4

reg 92 data e4

reg 93 data 9b

reg 102 data e2

工作在从模式,reg 8 D7、D6位需要配置为00;

工作在从模式应该不需要PLL产生时钟了,因为都有soc提供了。

您输入的音频信号 word length是多少bits的?这个要和BCLK和WCLK对应起来。

在datasheet Figure 10-2. Functional Block Diagram With Registers框图路径中含有对应的寄存器方便您配置,再尝试下看下是否可以输出?

下面文档也方便您配置:

| TLV320AIC3104 Programming Made Easy |

word length =16

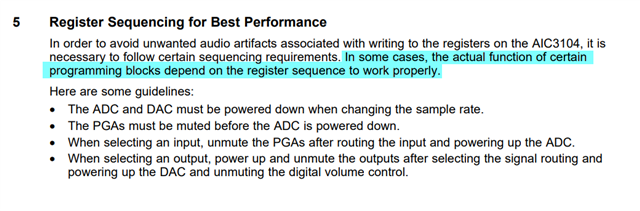

您好,我这边声音出来了,但是有一个问题,我这边用agmplay工具播放的时候,然后把下面寄存器写入才会有声音输出,当我把这些寄存器集成到代码然后去播,不出声音。帮忙定位一下问题,还有寄存器设置有顺序要求吗?

echo 1,80 ;

echo 4,20 ;

echo 5,00 ;

echo 6,00 ;

echo 7,1e ;

echo 9,40 ;

echo 11,04;

echo 41,50;

echo 43,00;

echo 44,00;

echo 82,ef ;

echo 85,ef ;

echo 86,9b ;

echo 89,ef ;

echo 92,ef ;

echo 93,9b;

echo 8,00 ;

echo 102,a2;

echo 3,11 ;

echo 3,91 ;

echo 37,c0;

很高兴有了进展;

工作在从模式应该不需要PLL产生时钟了,因为都有soc提供了。

很抱歉这里说错了,这里还是需要产生ADC和DAC的采样时钟的,因此输入时钟不合适的话还是需要PLL产生合适的采样时钟信号的。

我不了解 agmplay这个工具,它是实现的什么功能?它提供数字音频信号源吗?

当我把这些寄存器集成到代码然后去播,不出声音。

“集成到代码”具体什么意思?您是否读出来以确认已写入寄存器?

上面代码逗号前面是寄存器十进制地址,逗号后面是寄存器值吗?

还有寄存器设置有顺序要求吗?

有些影响:

我这边声音出来了,但是有一个问题,我这边用agmplay工具播放的时候,然后把下面寄存器写入才会有声音输出,当我把这些寄存器集成到代码然后去播,不出声音。帮忙定位一下问题,还有寄存器设置有顺序要求吗?

寄存器设置顺序一样吗?看下是否寄存器设置顺序造成的?

你好,我这边今天改了一下驱动的上电时序,以及驱动的reset,问题已经解决,我这遇到一个新问题,就是我想同时让LEFT_LOP、RIGHT_LOP和HPLOUT三路一起发声,但是我这里只能做到让LEFT_LOP、RIGHT_LOP这两路同时发声,HPLOUT不能做到同时发声,麻烦您帮我看一下,我需要配置那些寄存器以及怎么设置可以解决这个问题?

逗号前面寄存器(十进制),后面是data(十六进制),如果要让三路同时播放,41寄存器和37寄存器怎么配置?以及还有其他相关的寄存器

1,80

4,20

5,00

6,00

7,1e

9,40

11,04

41,50

43,00

44,00

82,ef

85,ef

86,9b

89,ef

92,ef

93,9b

8,00

102,a2

3,11

3,91

37,c0

您好,按照您的建议,我已经设置了相关寄存器,并且我把reg=37的data分别设置成e0(single-ended)和d0(vcm),但是还是没有声音输出。

我把寄存器37设置c0,寄存器47,82,92都设置成0x80后,然后就有声音了,这个我有点不太明白了哈?希望指教,谢谢

1,80

3,91

4,20

5,00

6,00

7,1c

8,00

9,40

11,04

37,e0

41,00

43,00

44,00

47,80

50,ef

51,9d

82,80

85,ef

86,9b

89,ef

92,80

93,9b

102,a2

,但是我41寄存器设置成0x50切换到DAC_L3和DAC_R3后,寄存器82,92都是音量控制寄存器设置为117有声音,设置成00就没有声音了,

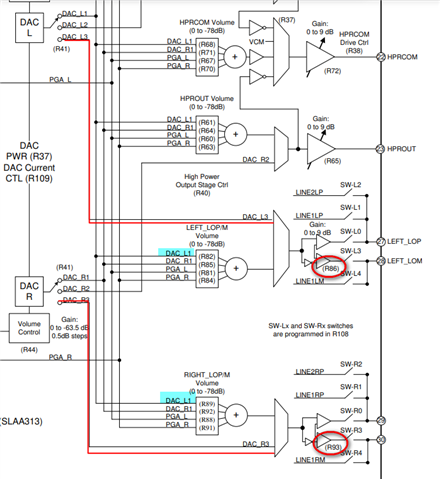

看下面路径框图,DAC输出设置到DAC_L3和DAC_R3后,音量大小不受寄存器82,92控制,因为信号路径不经过这里,音量受寄存器86和93控制:

但是我41寄存器设置成0x50切换到DAC_L3和DAC_R3后,寄存器82,92都是音量控制寄存器设置为117有声音,设置成00就没有声音了,

所以在这个测试中,将DAC输出设置到DAC_L3和DAC_R3后,寄存器改变的仅是R82,R92这两个寄存器吗?

41寄存器设置成0x00切换到DAC_L1和DAC_R1后,寄存器82,92都是音量控制寄存器设置为117没有声音,但是设置成00就有声音了。

寄存器82,92都是音量控制寄存器设置为117没有声音,是因为这里配置衰减的幅值太大,将信号衰减到极小,就没有声音输出了。

我有些奇怪,因为将DAC输出设置到DAC_L3和DAC_R3后,音量大小不受寄存器82,92控制,因为信号路径不经过这里。

但是我41寄存器设置成0x50切换到DAC_L3和DAC_R3后,寄存器82,92都是音量控制寄存器设置为117有声音,设置成00就没有声音了,

有声音时寄存器82,92具体配置的是什么? 有声音是指有效音频信号还是噪声?