Hi ti team,

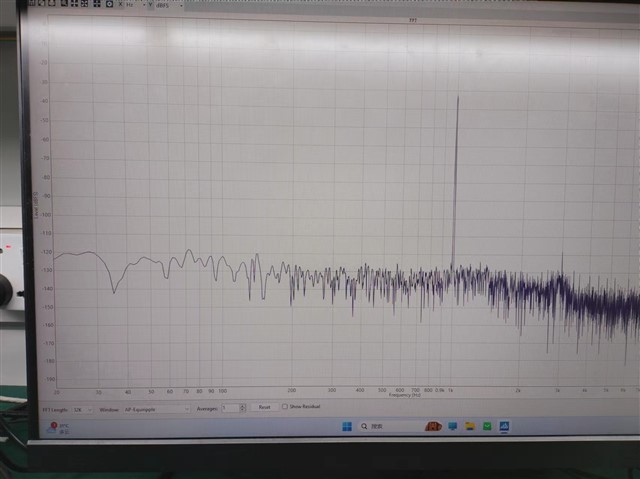

目前在测试5mvRMS输入的时候,THD+N 在0.2%以下,但是使用频谱看的时候干扰比较大,如下图片1.

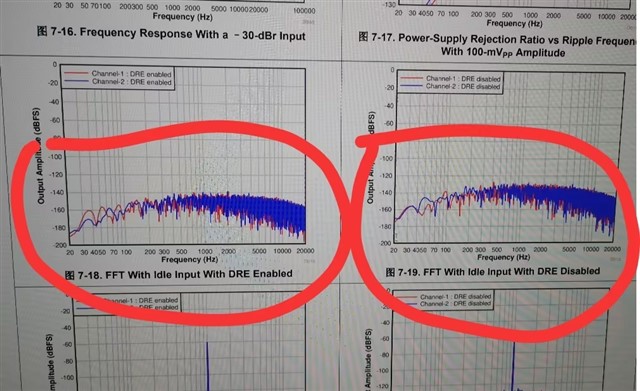

根据芯片手册打开DRE会有助于优化这个问题.0x3c寄存器写0x25,0x6d寄存器写0x81,测试没有改善,麻烦帮忙看一下,感谢!附件是TLV320ADC5120初始化代码.

void TLV320ADC_Init(void)

{

//w 9c 00 00 # Goto Page 0

//w 9c 02 81 # Wake-up device by I2C write into P0_R2 using internal AREG

//w 9c 6B 05 # Linear Phase Filter with 2 channel summer mode (DSP_CFG0)

//w 9c 07 30 # TDM Mode with 32 Bits/Channel

//w 9c 73 c0 # Enable Ch.1 - Ch.2

//w 9c 74 c0 # Enable Ch.1 - Ch.2 ASI Output channels

//w 9c 75 e0 # Power up ADC

u8 r_data;

u8 wack;

TLV320ADC_i2c_init();

wack = TLV320ADC_IIC_WriteReg(0x00,0x00);

if(wack == 0)

my_dump_str_data(1,"============set page0 fail", 0, 0);

if(wack == 1)

my_dump_str_data(1,"============set page0 succ", 0, 0);

TLV320ADC_IIC_WriteReg(0x02,0x81); // Wake-up device

TLV320ADC_IIC_WriteReg(0x6b,0x01); //

//ADC_IIC_WriteReg(0x07,0x30); // TDM Mode with 32 Bits/Channel

//TLV320ADC_IIC_WriteReg(0x07,0x40); // IIS Mode with 16 Bits/Channel

TLV320ADC_IIC_WriteReg(0x07,0x60); // IIS Mode with 24 Bits/Channel

TLV320ADC_IIC_WriteReg(0x13,0x01); // MCLK = 12.288 MHz, slave mode, auto clock configuration is enabled, automatic mode pll, fs is 48KHz

TLV320ADC_IIC_WriteReg(0x14,0x44); // BCLK = 3.072 MHz , 48KHz

// channel 1 config

//TLV320ADC_IIC_WriteReg(0x3c,0x24); // Analog single-ended input, AC-coupled input 10-k input impedance

//TLV320ADC_IIC_WriteReg(0x3c,0x04); // Analog differential input 10-k input impedance, analog differential input, dre/agc/drc disabled

// DRE or AGC or DRC enabled based on the configuration of bit 3 in register 108(P0_R108)

TLV320ADC_IIC_WriteReg(0x3c,0x25); // Analog single-ended input, AC-coupled input 10-k input impedance

TLV320ADC_IIC_WriteReg(0x6d,0x81); // Input signal level threshold is -60 db, Maximum gain is 4 db

// TLV320ADC_IIC_WriteReg(0x3d,(0<<1));// Channel gain is set to 0 dB

//TLV320ADC_IIC_WriteReg(0x3d,(12<<1));// Channel gain is set to 6 dB

//TLV320ADC_IIC_WriteReg(0x3d,(6<<1));// Channel gain is set to 3 dB

TLV320ADC_IIC_WriteReg(0x3d,(0<<1));// Channel gain is set to 0 dB

TLV320ADC_IIC_WriteReg(0x3e,0xc9); // Digital volume control is set to 0 dB

//TLV320ADC_IIC_WriteReg(0x3e,205); // Digital volume control is set to 2 dB

//TLV320ADC_IIC_WriteReg(0x3e,0xff); // Digital volume control is set to 27 dB

//TLV320ADC_IIC_WriteReg(0x3f,0x80); // Gain calibration is set to 0 dB

//TLV320ADC_IIC_WriteReg(0x40,0x00); // No phase calibration

TLV320ADC_IIC_WriteReg(0x73,0x80); // Enable Ch.1

TLV320ADC_IIC_WriteReg(0x74,0x80); // Channel 1 output slot is enabled

TLV320ADC_IIC_WriteReg(0x75,0xe0); // Power up ADC, PLL, MICBIAS

}

另外,还有如下几个问题,想深入了解一下,以让我司产品达到性能最优:

1、这个ADC通道相加模式是怎么理解的?

2、是否支持双通道输入,即IN1P和IN2P_GPI1并联、IN1M和IN2M_GPO1并联。就是说2个音频模拟通道是否可以并在一起?软件上怎么配置?我没有看到这个寄存器。

备注:如果adc 芯片支持立体声输入且两路模拟增益能独立设置,一路高模拟增益 一路低模拟增益,小信号的时候走高模拟增益一路。

3、同一时间AGC、DRC、DRE只能使能一个。打开DRE,THD+N失真会更小,是吗?

要打开DRE,就是设置0x6d寄存器就好了,对吧?这个DRE是监控内部信号的amplitude,并且相应调整内部PGA增益大小。这个DRE触发门限level,是只高于这个门限值就自动调整内部PGA增益,是吗?

4、TLV320ADC5120有调整PGA增益和数字音量大小,调整这2个参数都可以影响到整体链路增益,一般是调整PGA吧?调整PGA和数字音量大小的具体区别?

图片1:

图2