Part Number: LMX2595

Other Parts Discussed in Thread: LMX2581, LMX2541, LMX2485E, LMX2485, LMX2485Q-Q1, OPA211

Dear TI Technical Support Team,

I am designing a wideband RF signal source covering the full range of the LMX2595. My primary design challenge is minimizing close-in fractional spurs across the entire tuning range. I am evaluating a cascaded dual-LMX2595 architecture to address this.

Proposed Strategy (Tunable Reference): I intend to use a "Smart Reference" approach:

-

1st Stage LMX2595 (Fractional / Fine Tune): Acts as a variable reference source. It operates in Fractional Mode, generating a tunable output (e.g., varying between 80 MHz and 150 MHz).

-

2nd Stage LMX2595 (Integer / Multiplier): Acts as the main LO. Ideally, this stage operates in Integer Mode (or optimal fractional mode) to avoid generating its own close-in spurs.

-

Concept: To tune the final output, I will adjust the 1st stage frequency so that the 2nd stage can maintain an Integer-N relationship (or optimal PFD ratio) with the target output frequency.

Questions:

-

Feasibility: Is this "Tunable Reference" cascaded architecture recommended for wideband applications where the output is not fixed?

-

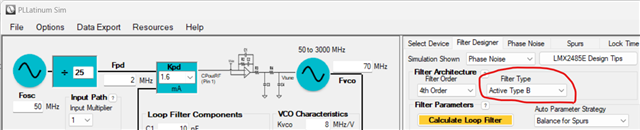

Filtering Challenge: Since the interface frequency between Stage 1 and Stage 2 is variable, I cannot use a fixed narrowband filter (like a SAW or Crystal). Would a simple Low Pass Filter (LPF) combined with a very narrow Loop Bandwidth (< 10 kHz) on the 2nd stage be sufficient to suppress the fractional spurs generated by the 1st stage?

-

Spur Propagation: Since the 2nd stage acts as a high-gain multiplier (20logN), any spur from the 1st stage is amplified. Does TI have any recommendations or frequency planning algorithms (possibly within TICS Pro) to calculate optimal "Reference vs. N-Divider" combinations? The goal is to push the 1st stage spurs far enough out so they are attenuated by the 2nd stage's loop filter.

-

Alternatives: For wideband low-spur requirements, is there a better configuration than cascading two devices? (e.g., Using the onboard Multiplier with dynamic PFD shifting on a single chip).

Thank you for your guidance.

Best regards,

RX