- 使用LMK04808B芯片对不同block的输出进行delay控制,经过sync事件后的输出先后顺序没有发生变化,这是为什么?器件除外dual pll internal模式下,启用了全通道的adelay ,全通道的时钟输出除了先后顺序,均满足我的设置。请教下为什么会出现这种问题。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好, 您是如何产生的sync, manula还是automatic?首先参考8.3.9.3.2 Methods of Generating SYNC 部分介绍的产生sync的方法。

其次,建议您参考8.3.9.3.4 SYNC Timing章节的介绍,参考FIgure11 和Figure12的时序。

也建议您将sync之后的波形附上看下,便于分析。

您好,关于之前提到的问题,我的sync是外部产生的,并且问题已经得到解决。

目前面临的新问题是,我以一块LMK04808B作为主时钟,生成多路100M的LVDS时钟,多路100M的时钟作为其余几块LMK04808B芯片的clkin输入时钟,目前产品的现象是,主芯片可以lock,但从芯片无法lock,具体为PLL2_DLD为高,PLL_1DLD为低。

除了主芯片的输入时钟为200M的LVDS的有源晶振,从芯片的输入时钟来自主芯片以外,主从芯片的其余外围电路均一致,PLL1的VXCO为122.88Mhz的CVHD950压控晶振。

在示波器上发现在从芯片的接收端的时钟抖动略大于主芯片的发送端。

是否是由于主芯片输出不够稳定导致从芯片无法锁定,如何能解决这一问题呢?

您好,抱歉回复晚了,下次如果有新问题咨询,为了能尽快回复给您,建议重新发贴。

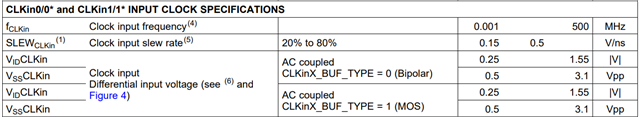

关于您的第二个问题,对输入时钟的要求如下,可以看到并没有对jitter有特别的要求,另外输出的LVDS作为从芯片的输入时钟,那么输入端是否

有端接100ohm 匹配电阻?