Part Number: LMX2595

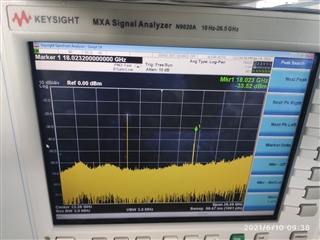

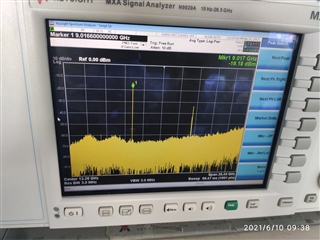

我想要出来18G的频率,为什么会出现这种情况,该怎么解决

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

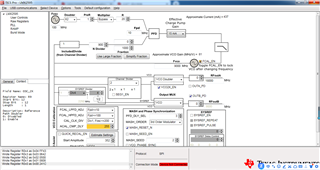

您好,您是按照TICSPro这里的寄存器配置的得到输出波形是吗?

在您的配置里,配置的都没问题,看到ACAL_CMP_DELAY 您这里的值设为255,我试了下,好像不能超过10.

因为看了下这里的定义,ACAL_CMP_DLY>Fmsclk/10即可,而where Fsmclk = Fosc / 2^ CAL_CLK_DIV, CAL_CLK_DIV设的为1, 所以Fsmclk=50Mhz,ACAL_CMP_DLY>5就可以。 您这两个图分别是在VCO和VCO doubler的条件下得到的输出吗?

您好, 麻烦将小数模式的配置附上看下?

另外,ACAL_CMP_DELAY建议设置为5, 因为使用auto VCO calibration时候,建议使用默认参数,不要更改。

另外在您的第一张TICSpro中,Fpd是10Mhz是吗? 您是使用的自己的板子+TICSpro 软件帮助配置的是吗?

您好,相位噪声这么大的主要原因有三点:

1:杂散频率是1Khz的倍数。2.fPD鉴相频率太小了。 3.使用的三阶调制。

如果使用10Mhz的鉴相频率的话,那么使用1阶调制的相位噪声最小,如果是三阶调制的话,鉴相频率使用100Mhz的噪声噪声最小。