Part Number: CDCLVD1208

目前我们在使用CDCLVD1208这个TI的时钟芯片时,输入差分时钟,但是输出丢失一部分时钟数据。主要是想了解CDCLVD1208这个芯片的fail-safe function是否会对输出信号有影响?谢谢!

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: CDCLVD1208

目前我们在使用CDCLVD1208这个TI的时钟芯片时,输入差分时钟,但是输出丢失一部分时钟数据。主要是想了解CDCLVD1208这个芯片的fail-safe function是否会对输出信号有影响?谢谢!

在CDCLVD1208的手册中,有说:

The part supports a fail-safe function. The device incorporates an input hysteresis which prevents random oscillation of the outputs in the absence of an input signal.

实际我们在使用的时候发现,时钟发生器正常发送时钟时,通过CDCLVD1208是正常输出,但是中间暂停时钟发生器的时钟后,再开启,对比CDCLVD1208的输入和输出时钟,发现输出的时钟丢失5-6个周期的信号,想了解这方便具体是什么原因导致的?

谢谢!

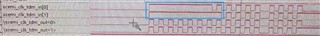

我们的产品应用是在EMU上使用,时钟的产生和接收,是通过FPGA产生的,目前我们通过signal_tap抓取到的信号如下图:

其中clk_tdm_in代表经过clk mux后输入到FPGA的信号,clk tdm out代表由fpga生成到clk mux的信号。

图中蓝色线标记的部分,就是丢失的时钟信号。

FPGA产生clk tdm out0,经过CDCLVD1208,再输出clk tdm in0到FPGA内部,我们跑的时钟才20MHz。

以上是从硬件上测量时钟波形,我们正尝试做一块验证板来测量此信号,不过需要花点时间,所以希望先沟通看是否能解决,谢谢!

CDCLVD1208输出丢失时钟信号之前,是进行的时钟发生器暂停操作吗?再开启时钟发生器后,CDCLVD1208没有时钟输出,等待5-6个周期的信号才有输出?

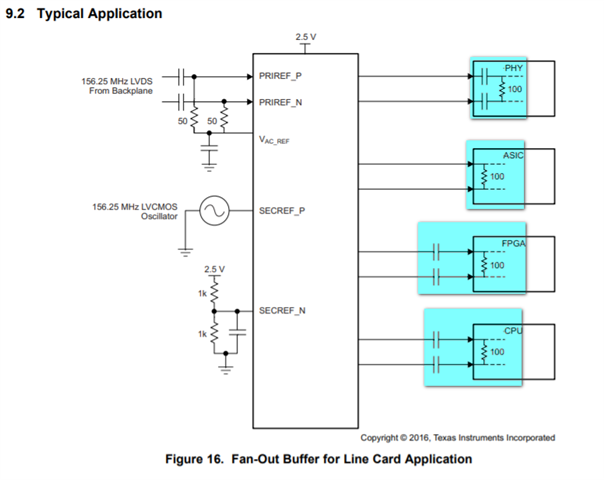

CDCLVD1208需要适当的偏压和端接,以确保设备的正确工作。 TI 建议将终端电阻器放在靠近接收器的位置。 如果接收器内部偏压的电压与 CDCLVD1208 的输出共模电压不同,则必须使用交流耦合。如果 LVDS 接收器具有内部 100Ω Ω 端接,则必须忽略外部端接。数据手册9.2章节列了几种接收端的情况,请检查是否连接正确