Part Number: CDCLVD2104

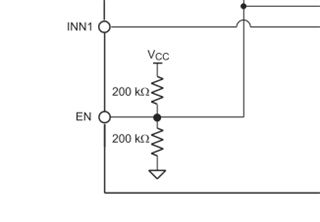

问题1:

本时钟芯片的输入采用AC耦合,见下图,但在我们应用中存在一种异常情况,即源LVDS驱动器件(CDCD62005)其驱动输出处于高阻状态,即没有输出。

请问此时CDCLVD2104芯片的输出处于什么状态?(EN处于使能输出的状态)

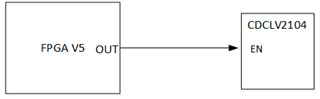

问题2:

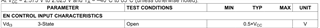

在我们应用中CDCLV2104的EN管脚由FPGA控制,默认FPGA输出高阻,CDCLV2104输出使能。但EN管脚手册描述是由200K的上下拉组成的,0.5VCC即判断为输出使能。

此时FPGA(V5系列)输出高阻,其手册仍描述会有最大10uA的漏电流,可能会导致EN电压偏离0.5VCC较远。

请问FPGA输出高阻→EN使能所有输出此方案是否存在风险?

如有风险应该如何处理呢?