10M由授时时钟经单端转差分从clkin0口输入,61.44M是差分VCXO从OSCin输入,PLL1_R设定为125,PLL1_N设定为768,鉴相频率80KHz,CPout1通过一个2阶的低通接到了VCXO的VX管脚,10M的Vpp是600mV,61.44M的Vpp是360mV,目前板子上电以后PLL1有时候能锁定有时候不能锁定,请教各位大侠,这是什么原因?有什么解决办法?多谢

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

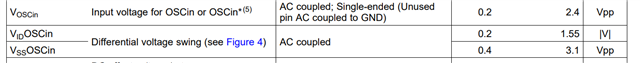

您好,OScin差分输入的话,Vid的电压swing范围是0.4~3.1Vpp,您这里给的是360mV,要求最低400mV。 CLKIN0的Vid=600mV是满足的,所以我怀疑PLL1不稳定的原因是由于OSCin的输入问题导致。

您好,PLL2一直是稳定的吗?如果是的话我的建议是可以尝试交换一下PLL1和PLL2的loop filter gain,看是否还是PLL1 unlock?

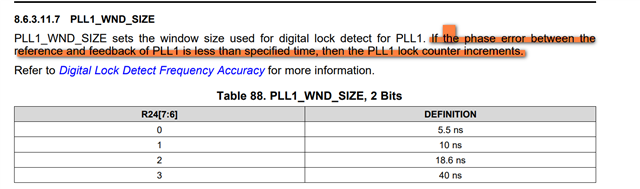

另外,就是修改PLL1_WND_SIZE为18.6ns试试,我看您配置的是40ns,这里的问题应该不大。