Part Number: LMX2595

(2) LMX2594: LMX2594:手动ramp模式出现许多杂波 - 时钟和计时论坛 - 时钟和时序 - E2E 设计支持 (ti.com)

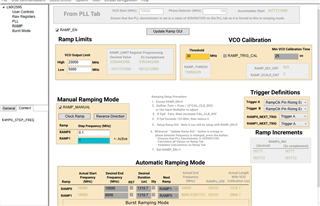

For waveforms that are NOT calibration free, the slew rate of the ramp must be kept less than 250 kHz/µs. Also,

for all automatic ramping waveforms, be aware that there is a very small phase disturbance as the VCO crosses

over the integer boundary, so one might consider using the input multiplier to avoid these or timing the VCO

calibrations at integer boundaries.

对于不是免校准的波形,斜坡的压摆率必须保持小于 250 kHz/µs。 此外,对于所有自动斜坡波形,请注意当 VCO 越过整数边界时会出现非常小的相位干扰,因此可以考虑使用输入乘法器来避免这些或在整数边界处对 VCO 校准进行定时。

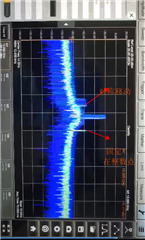

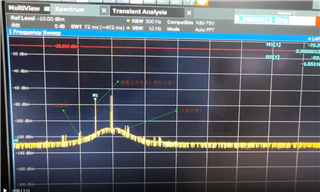

对于手动RAMP出现的在整数倍鉴相FPD频率处出现的杂波是否是相位干扰,(整数边界杂散),这对于连续性的相位是否有影响,而且此处的杂波是一根在整数倍fpd出现,还有一根在主信号另外一侧对称出现。

请问这种整数边界杂散有无规避或者消除减弱的方法?请问初始的mash的阶数对此整数边界再RAMP模式下的影响有没有定量数据展示。

请问这种整数边界杂散有无规避或者消除减弱的方法?请问初始的mash的阶数对此整数边界再RAMP模式下的影响有没有定量数据展示。