我司后续生产的加速卡,在配置时钟的时候,存在些问题,可以麻烦帮分析一下吗

时钟芯片: CDCI6214RGER

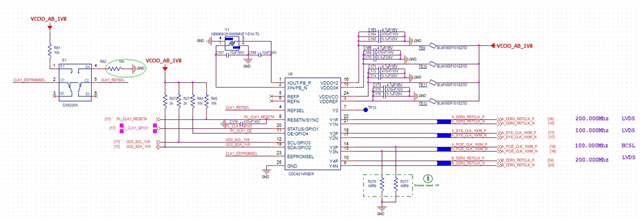

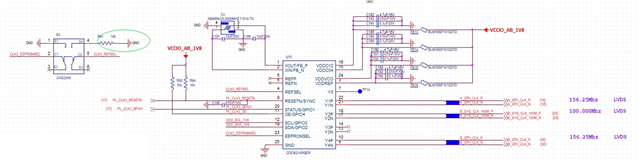

原理图设计:同一个板上使用两颗该芯片U9,U10,使用同一个I2C去配置,U9使用EEPROM page1, U10使用Page0,均采用25MHz晶振作为时钟输入源,默认状态是Fallback模式(EEPROMSEL pin/REFSEL floating)

U9:CH1 LVDS 200MHz

CH2 LVDS 100MHz

CH3 HCSL 200MHz

CH4 LVDS 200MHz

U10:CH1 LVDS 156.25MHz

CH2 LVDS 100MHz

CH3 LVDS 125MHz

CH4 LVDS 156.25MHz

原理图如图片,附件为U9 配置寄存器值:

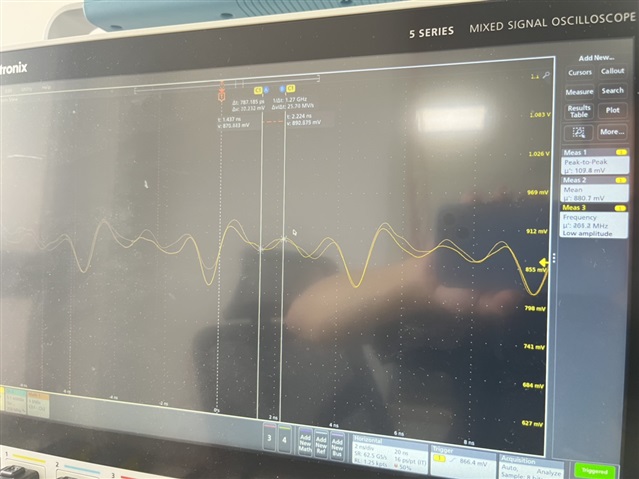

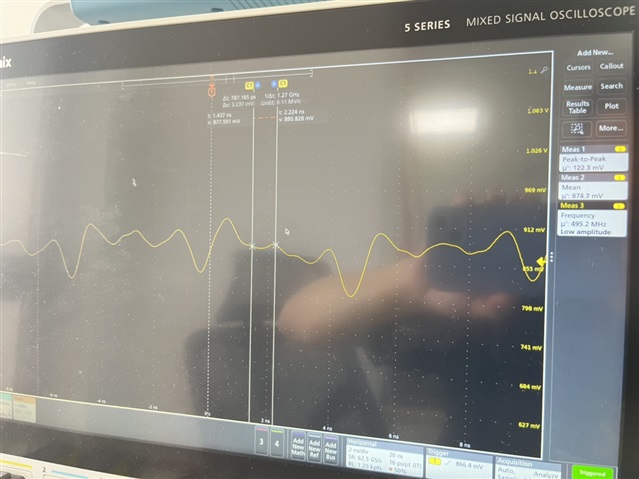

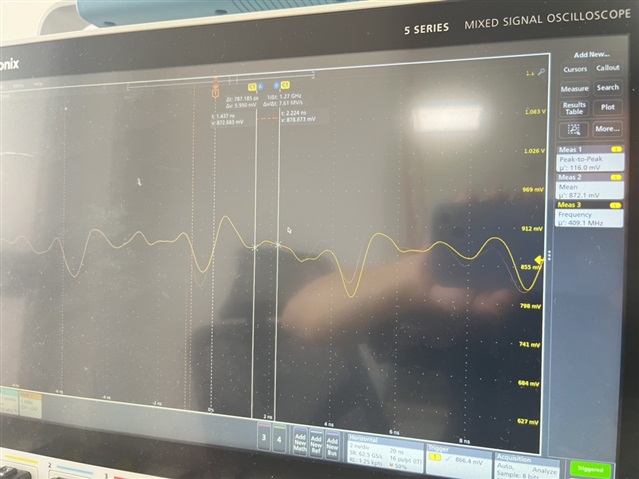

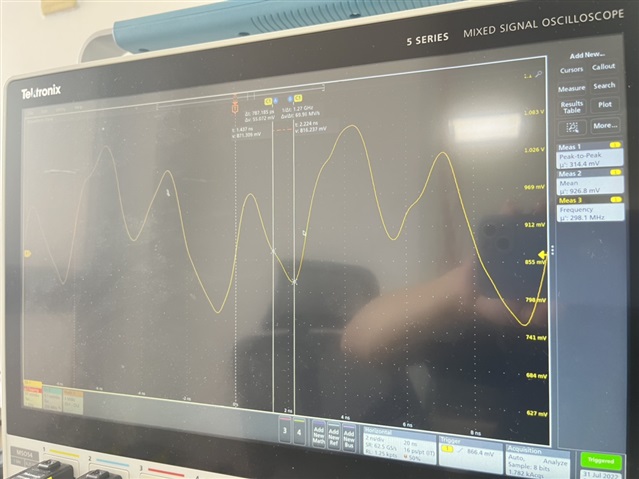

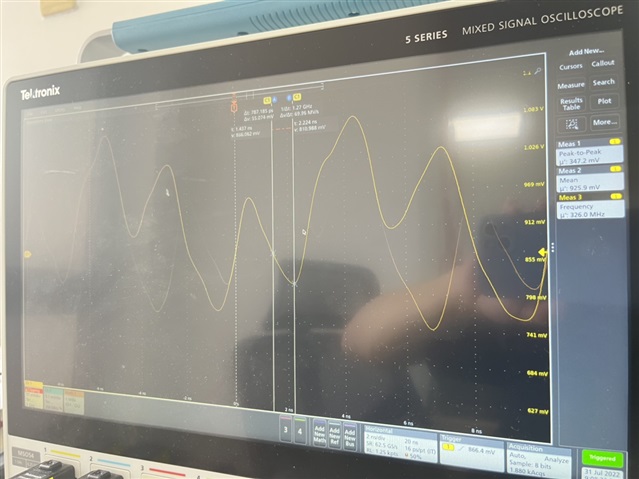

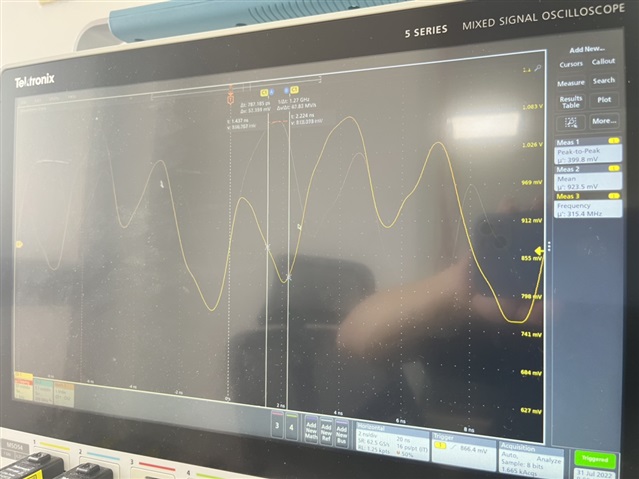

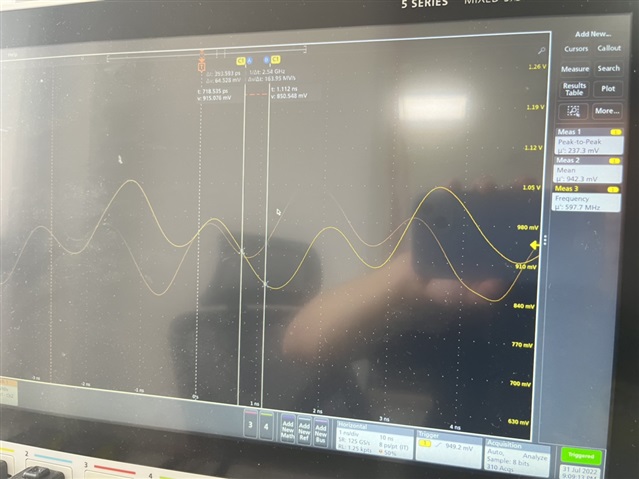

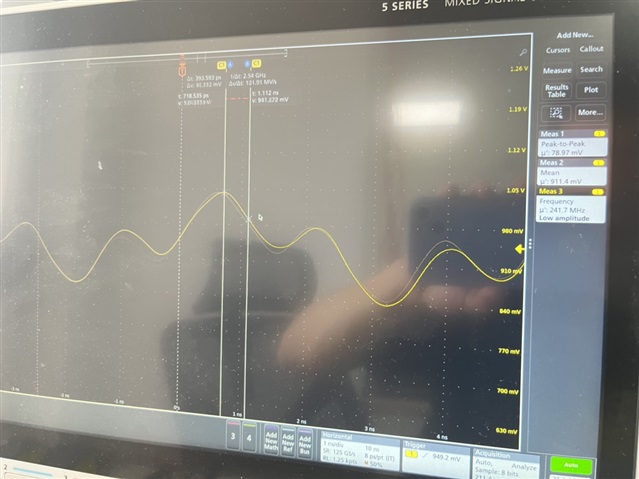

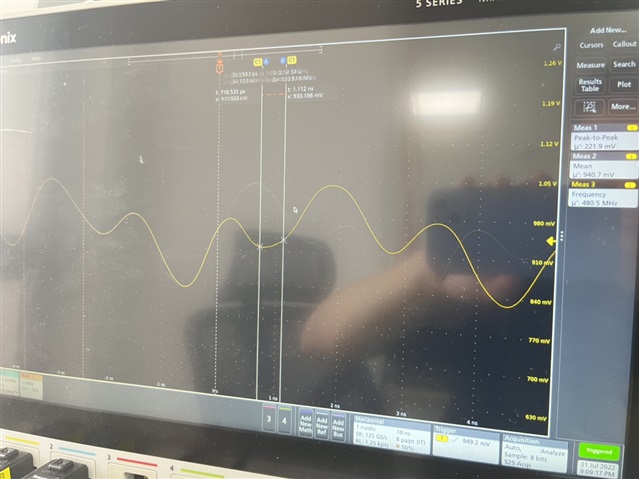

- U10目前配置成功,U9 只有通道3输出正常,通道1,2,4,均有稳定波形,但是频率值不对。

R70 0x00460000 R69 0x00450000 R68 0x00440000 R67 0x00430020 R66 0x00420200 R65 0x00410F34 R64 0x0040000D R63 0x003F0210 R62 0x003E4209 R61 0x003D1500 R60 0x003C0018 R59 0x003B102B R58 0x003A0008 R57 0x00390A65 R56 0x00380405 R55 0x00370003 R54 0x00360000 R53 0x00358000 R52 0x00340008 R51 0x00330A65 R50 0x00320409 R49 0x00310006 R48 0x00300000 R47 0x002F8000 R46 0x002E0008 R45 0x002D0A65 R44 0x002C0405 R43 0x002B0006 R42 0x002A0000 R41 0x00298000 R40 0x00280008 R39 0x00270A65 R38 0x00260409 R37 0x00250006 R36 0x00240000 R35 0x00238000 R34 0x00220050 R33 0x00210007 R32 0x00200000 R31 0x001F1E72 R30 0x001E5140 R29 0x001D000C R28 0x001C0000 R27 0x001B0400 R26 0x001A0A18 R25 0x00190000 R24 0x00180001 R23 0x00170000 R22 0x00160000 R21 0x00150000 R20 0x00140000 R19 0x00130000 R18 0x00120000 R17 0x001126C4 R16 0x0010921F R15 0x000F5037 R14 0x000E0000 R13 0x000D0000 R12 0x000C0000 R11 0x000B0000 R10 0x000A0000 R9 0x00090000 R8 0x00080000 R7 0x00070000 R6 0x00060000 R5 0x00050008 R4 0x00040055 R3 0x00039800 R2 0x00020053 R1 0x00016822 R0 0x00001010