我这边使用lmk04821,工作在Dual-pll cascaded zero-delay mode, TICS pro配置文件为lmk04821_config.tcs,参考时钟输入为10MHz、5dBm正弦波,从CLKin1输入。通过FPGA抓取芯片IO输出的PLL_DLD信号。发现PLL1偶尔会失锁,失锁后大约0.16ms再锁定;PLL2始终锁定。请问PLL1失锁的原因可能是什么,是否是配置不对。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

我这边使用lmk04821,工作在Dual-pll cascaded zero-delay mode, TICS pro配置文件为lmk04821_config.tcs,参考时钟输入为10MHz、5dBm正弦波,从CLKin1输入。通过FPGA抓取芯片IO输出的PLL_DLD信号。发现PLL1偶尔会失锁,失锁后大约0.16ms再锁定;PLL2始终锁定。请问PLL1失锁的原因可能是什么,是否是配置不对。

您好,

为更加有效地解决您的问题,我已将您的问题发布在E2E英文技术论坛上,请更了解这款芯片的TI资深工程师为您解答,请耐心等待他们的回复:

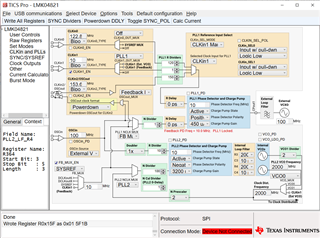

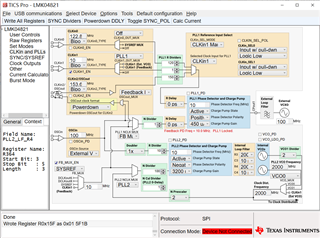

查看您的TIC Pro文件后,我认为问题可能是您的SYSREF设置不正确。如果您转到SYNC/SYSREF选项卡,然后查看窗口右侧,您的SYSREF_CLR是启用的,如果您要获得SYSREF输出,则不应启用SYSREF (请注意红色的消息)。确保取消选中该框。内部发生的是寄存器确保不会出现不需要的脉冲(有关此信息,请参阅数据表第41页),这可能是您的PLL1从解锁状态进入锁定状态的原因。

如果不是这样,我相信这种锁定状态的变化可能来自外部环路滤波器的设计方式。因此,在您的回复中,请确保包含该信息(电阻和电容器值,使用的拓扑,所需的回路带宽以及外部VCO增益或数据表),以便为您提供最佳支持。您还可以使用TI的PLLatinum SIM工具,根据您的环路带宽和外部VCO增益来设计环路滤波器(可在此处下载)。