Part Number: LMK1C1104

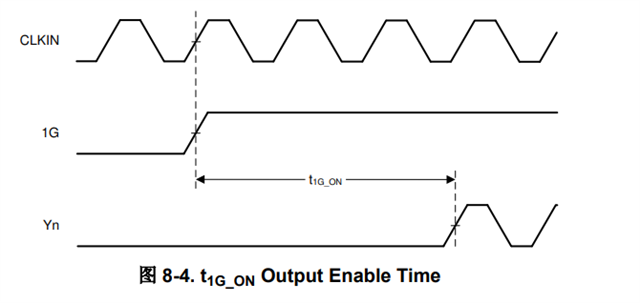

这个好像是回复问题就自动更新状态为已解决么? 还在debug中。 我也是想确认下Buffer会在什么时候使能?看SPEC描述的是只在1G上升沿后最多延迟5个cycle就会使能(tSTART)。 确定不需要考虑CLKIN的上升沿么?看SPEC的图8-4好像是Trigger要同时看CLKIN和1G的上升沿吧,而且假如不管CLKIN的有无,那么cycle的频率时长又如何确定呢?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好,

您在回复问题的时候,看下回复对话框右下角是否勾了“问题已解决”,对应的我们的对话框是“TI认为已解决”,如下截图,回复的时候把这个√去掉。

您的理解应该是对的,5个 cycles应该是指CLKIN的5个周期,在1G高电平的同时需要CLKIN的上升沿才能使能,至少需要1个CLKIN 周期(cycles),最多5个CLKIN 周期(cycles)。如果是1个CLKIN cycle,输出端则会损失一个CLKIN,如果是5个CLKIN cycles,输出端则会损失5个CLKIN cycles,因此为了保证所有设备都能正常工作,CLKIN 输入端至少需要提供5个多余的CLKIN cycles来保证使能buffer。这样就会存在一个问题,因为不知道具体需要多少个CLKIN cycles能够使能buffer,所以需要至少提供5个多余的CLKIN cycles,使得输出端会有多余的不确定个数的CLKOUT cycles,不知道这会不会对您设备的工作产生影响。

另外,我想知道您测试了几个设备是这个现象?这个现象在每个设备上都存在吗?