This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

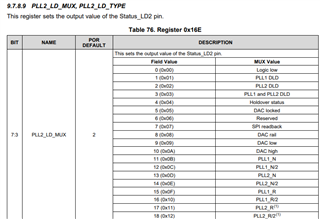

STATUS_LD2,默认的是PLL2 lock输出引脚,当PLL2 lock时,输出为高电平。其次这个引脚的功能可通过下面这个0x16E寄存器去配置,可以配置为open drain或push pull output。

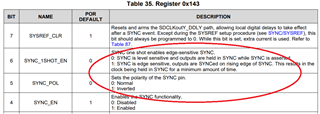

sync是对边沿敏感还是极性敏感也是通过寄存器来配置的,比如电平高低敏感,则bit6=0. 高电平bit5=0,低电平的话bit5=1

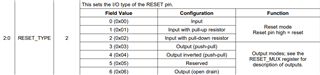

reset 也一样,作为输复位引脚,也是通过寄存器来RESET_TYPE配置。

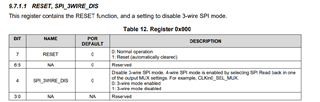

您好,您可以只使用三线SPI mode。SDIO也可以通过寄存器配置为输出模式。

或者您也可以disable 3 wire模式,使用传统的4 wire SPI模式,通过CLKin_SEL_MODE来选择哪路输出作为回读。

您好,抱歉我不清楚您说的mode 0和mode3具体指的是什么。

但是对于LMK04821的SPI时序来说,从CS由高到低转换开始,SPI slave被选通,然后经过tCS时间为SCLK的建立时间。

我的建议参考每块芯片的数据手册,包括时序,电气性能等。 按照数据手册中给出的时序或电气参数去使用,才能保证它的最佳性能。

明白您的意思了,那我们的这款LMK04821 首先是不能配置SPI 这四种模式的。

其次这个时序确实开始,是SCLK的相位和极性都是0,即mode0,最后又是mode 3,我理解的是这个时序目的只是想告诉mode0和mode3的条件下tCS和tCH的时间要求。或者说这两种mode0和mode3都是支持的。我个人是这么理解这个时序的。