Part Number: LMK61E07

在使用中我发现在Autostart启用时,将LMK61E07由100M配置为125M后实际输出频率为130M+。

在未启用Autostart时复位PLL并重新置位Autostart或置位Calibration可输出正确的频率。或写入PLL配置后复位两次PLL也可输出正确频率。

请问是否是我的操作步骤有问题导致了该现象。

以下是可复现现象的Linux Shell脚本

配置为100M

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: LMK61E07

在使用中我发现在Autostart启用时,将LMK61E07由100M配置为125M后实际输出频率为130M+。

在未启用Autostart时复位PLL并重新置位Autostart或置位Calibration可输出正确的频率。或写入PLL配置后复位两次PLL也可输出正确频率。

请问是否是我的操作步骤有问题导致了该现象。

以下是可复现现象的Linux Shell脚本

配置为100M

您是使用自己的方法对设备进行编程吗?您是否使用TIC Pro或 LMK61xx Oscillator Programming Tool 生成寄存器设置?或者您是否手动生成了设置?

从100M修改为125M的具体操作过程是什么?是否使用了EEPROM或SRAM?

在我看来,如果在100 MHz和125 MHz之间切换,那么您可以设置相同的VCO频率,这样您只需更改输出分频器(OUTDIV)来切换这两种情况,也就是只修改OUTDIV寄存器,无需VCO 复位以重新校准。

从100M修改为125M 修改了PLL和OUTDIV配置,以下为操作使用的Linux Sehll脚本,倒数第二个参数为写入的地址,倒数第一个为写入的数据:

i2ctransfer -y $i2c_index w2@$dcxo_addr 21 0x03

i2ctransfer -y $i2c_index w2@$dcxo_addr 23 0x28

i2ctransfer -y $i2c_index w2@$dcxo_addr 26 0x32

i2ctransfer -y $i2c_index w2@$dcxo_addr 36 0x08

i2ctransfer -y $i2c_index w2@$dcxo_addr 72 0x02

未使用EEPROM和SRAM,相同的配置写入EEPROM掉电重启后可输出正确的频率。

我只是想知道出现该现象的原因,以避免未来使用过程中可能遇到的问题。

我还是没明白LMK61E07的工作过程,它是不是这样的?您是先配置输出100MHZ,工作一段时间后(或延迟一段时间后),又做以上寄存器修改,期望LMK61E07 输出125MHZ的频率,结果实际输出频率为130M+?

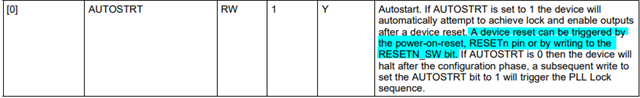

我注意到 LMK61E07没有RESETn pin和 RESETN_SW bit,那么触发 PLL Lock只能是上电复位(power-on-reset)。

是不是在没有使用EEPROM的情况下,没法使用Autostart功能?

我理解的是在没有使用EEPROM的情况下,没法使用Autostart功能。在100M配置变为125M配置后需执行Autostart值 0->1的这个过程,这样 PLL 才能Lock

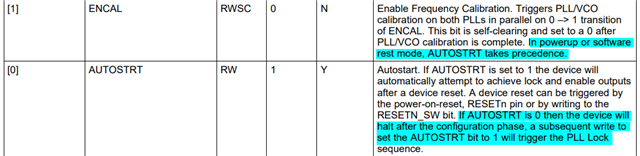

SWR2PLL bit也可触发PLL Lock,当未置位AUTOSTART时置位SWR2PLL,LMK61E07会没有输出,随后需要置位AUTOSTART或ENCAL,才会输出。

您这里是说SWR2PLL bit不能触发PLL Lock吧?

我理解的SWR2PLL、AUTOSTART和ENCAL的功能分别是这样的:

SWR2PLL需要在每次寄存器写入或更改后写1以 resets the PLL calibrator and clock dividers。这个是编程寄存器后必须的一个步骤。

在编程完寄存器后需要执行触发PLL Lock,这样PLL才能LOCK设备才能输出正确频率。

AUTOSTART和ENCAL都有触发PLL Lock的功能。AUTOSTART在置1时,配置完寄存器后将SWR2PLL置1后会自动触发PLL Lock。这是上电后一次自动的功能,如果再修改寄存器、SWR2PLL置1,设备不会再自动触发PLL Lock,那么输出频率就会不对,需要使用ENCAL来触发PLL Lock以输出正确频率。或者在需要配置寄存器修改输出频率前,将AUTOSTART置0,配置完寄存器和SWR2PLL置1后,再将AUTOSTART置1以触发PLL Lock输出正确频率。

这无法解释将频率由125M修改为100M时,进行一次RLL Reset 后 PLL即可Lock。

也无法解释将频率由100M修改为125M时,进行两次PLL Reset 后 PLL才能Lock。

以上两种情况,分别是在什么情况下触发PLL Lock的?如果与我上述描述功能相冲突,我再去确认下这几个寄存器位的功能。

据我测试AUTOSTART并非上电后一次性功能,因为在AUTOSTART置0时置1 SWR2PLL设备会停止输出而非频率不准。

频率不准仅在AUTOSTART置1时,将频率由100M修改为125M时置1 SWR2PLL后存在,在再次将SWR2PLL置1后输出频率正常。在仅写入PLL配置和OUTDIV而不操作SWR2PLL时输出频率为117M左右,与修改前的PLL频率/修改后的OUTDIV相等。

在AUTOSTART置1且SWR2PLL置1后ENCAL似乎无效,因为当输出频率不准时置位ENCAL输出频率不会发生变化,也不会触发PLL Lock,仅当AUTOSTART置0时SWR2PLL置1后置ENCAL才有效。

我的推测原因为在AUTOSTART置1时将频率由100M修改为125M,将SWR2PLL置1后AUTOSTART会自动触发PLL Lock与ENCAL,但不知什么原因导致无法成功Lock,当再次将SWR2RLL置1时,PLL成功Lock。

在AUTOSTART置1时

125M->100M: 写PLL与OUTDIV -> SWR2PLL -> Lock

100M->125M: 写PLL与OUTDIV -> SWR2PLL -> 输出频率不准 且 Loss of Lock PLL -> SWR2PLL->Lock

在AUTOSTART置0时

125M->100M: 写PLL与OUTDIV -> SWR2PLL -> 无时钟输出输出 -> AUTOSTART 或 ENCAL -> Lock

100M->125M: 写PLL与OUTDIV -> SWR2PLL -> 无时钟输出输出 -> AUTOSTART 或 ENCAL -> Lock

据我测试AUTOSTART并非上电后一次性功能,因为在AUTOSTART置0时置1 SWR2PLL设备会停止输出而非频率不准。

是的,在AUTOSTART置0时,配置完寄存器设备会停止:

频率不准仅在AUTOSTART置1时,将频率由100M修改为125M时置1 SWR2PLL后存在,在再次将SWR2PLL置1后输出频率正常

在这种情况下,即AUTOSTART置1时,且修改了频率配置时,应使用ENCAL bit 触发PLL LOCK,您是否可以尝试:置1 SWR2PLL后,置1 ENCAL bit是否可以lock?

在AUTOSTART置1且SWR2PLL置1后ENCAL似乎无效,因为当输出频率不准时置位ENCAL输出频率不会发生变化,也不会触发PLL Lock,仅当AUTOSTART置0时SWR2PLL置1后置ENCAL才有效。

在这种情况下,应该是AUTOSTRT takes precedence.即AUTOSTRT 优先级高,在AUTOSTRT =1时,ENCAL 无效。

In powerup or software rest mode, AUTOSTRT takes precedence.

在AUTOSTART置1时

125M->100M: 写PLL与OUTDIV -> SWR2PLL -> Lock

100M->125M: 写PLL与OUTDIV -> SWR2PLL -> 输出频率不准 且 Loss of Lock PLL -> SWR2PLL->Lock

在AUTOSTART置0时

125M->100M: 写PLL与OUTDIV -> SWR2PLL -> 无时钟输出输出 -> AUTOSTART 或 ENCAL -> Lock

100M->125M: 写PLL与OUTDIV -> SWR2PLL -> 无时钟输出输出 -> AUTOSTART 或 ENCAL -> Lock

这四种情况中,第1、3、4项都符合我上述理解描述,第2种情况,我认为您应该置1 ENCAL bit 来触发PLL LOCK,所以测试后请反馈给我是否可以得到正确输出?

这四种情况中,第1、3、4项都符合我上述理解描述,第2种情况,我认为您应该置1 ENCAL bit 来触发PLL LOCK,所以测试后请反馈给我是否可以得到正确输出?

在第2种情况

写PLL与OUTDIV -> SWR2PLL -> 输出频率不准 且 Loss of Lock PLL -> ENCAL -> 输出频率无变化且 Loss of Lock PLL

写PLL与OUTDIV -> SWR2PLL -> 输出频率不准 且 Loss of Lock PLL -> AUTOSTART置0 -> ENCAL -> 输出频率无变化且 Loss of Lock PLL

已得到的回复,他说包含ENCAL bit 和AUTOSTRT bit 的寄存器R10 (dev_CTL)可能已弃用,他正在确认这个寄存器的问题。

100M->125M: 写PLL与OUTDIV -> SWR2PLL -> 输出频率不准 且 Loss of Lock PLL -> SWR2PLL->Lock

关于这个现象,您是否知道出现这种现象的频率?他说他无法复现出这种现象。当他写入输出分配器寄存器时,输出频率发生了变化,之后触发SWR2PLL不会打破锁定或产生持续的错误输出频率。但是在触发SWR2PLL后,偶尔会在很短的时间内出现不正确的输出频率,但它会立即自行纠正。

已收到以下回复内容,美国的工程师说他还是无法复现您的现象,他希望您提供配置代码,以查看初始化寄存器配置和寄存器写入顺序。

I have learned that register R10 was inherited from an older product and there typically should not be a reason for customers to program it. The device's EEPROM by default has AUTOSTRT = 1, so the device will automatically calibrate its VCO after power-on and after manually triggering a software reset through the SWR2PLL bit, which is generally desired behavior. ENCAL manually triggers the VCO calibration but I think it makes more sense to use SWR2PLL instead, which exists in the fully supported register R72.

I ran some tests in the lab today using in the information you provided. First I configured my device to correctly output a 100 MHz HCSL signal using a N-divider of 0x2e (therefore VCO frequency of 4600 MHz) and output divider of 0x2e. I wrote 0x28 to R23 to change the output divider, the output signal became 4600 MHz / 40 = 115 MHz as expected. Then I wrote 0x32 to R26 to change the N-divider to decimal 50, the output signal deviated to around 116.42 MHz as expected (PLL has not been allowed to recalibrate yet). Finally I wrote 0x02 to R72 to trigger the SWR2PLL software reset and the correct output frequency of 125 MHz immediately appeared. So I was again unable to replicate the problem because I achieved a stable 125 MHz output after the first SWR2PLL reset.

I think it would help to have the customer's configuration code, I would like to check the initial register configuration and the subsequent writes for next week

已收到回复:

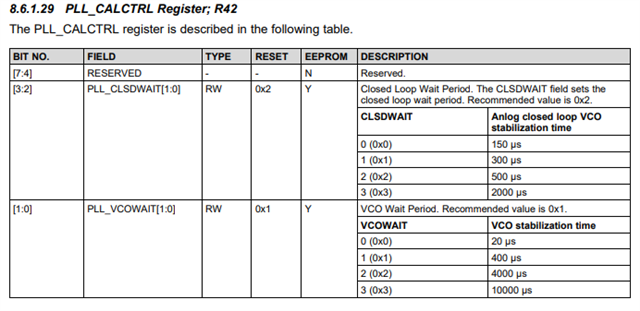

大意是 应该是将0x00写入寄存器R42导致的问题。

R42寄存器隐藏在GUI内部,因此是不打算让客户修改它的。将其写入0x00将模拟闭环稳定时间和VCO等待时间都设置为其最小值,这是不推荐的,并且在您启动软件重置后可能不会给VCO足够的时间来正确重新校准。如果您在更改输出频率之前的任何时间点运行reset(),或者该寄存器值已写入EEPROM,则这可能是导致此现象的原因。

建议根据数据表,将R42的值写入推荐/默认值,应为0b00001001=0x09。修改后看是否解决此问题?如果可以的话,请确保R42在EEPROM中具有正确的值0x09,并避免将来对其进行修改。

修改R42值后已解决问题。

但是我发现Data sheet中,Reg map和Reg description中reset值不同,且两套值均无法输出默认频率70.656MHz,Reg map中的值甚至超出了PLL输出频率上限。

以下是我发现的不同

| Reg | 17 | 26 | 34 | 36 | 42 |

| ------------------------- | ---- | ---- | ---- | ---- | ---- |

| Reg map reset val | 0x00 | 0x64 | 0x24 | 0x28 | 0x00 |

| Reg description reset val | 0x80 | 0x32 | 0x28 | 0x08 | 0x09 |