Part Number: CDCE813-Q1

你好

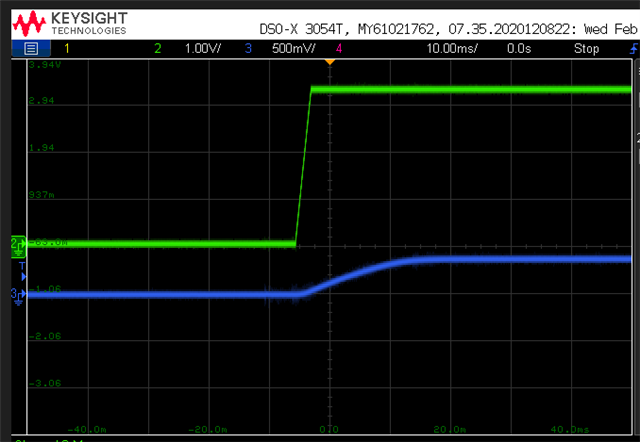

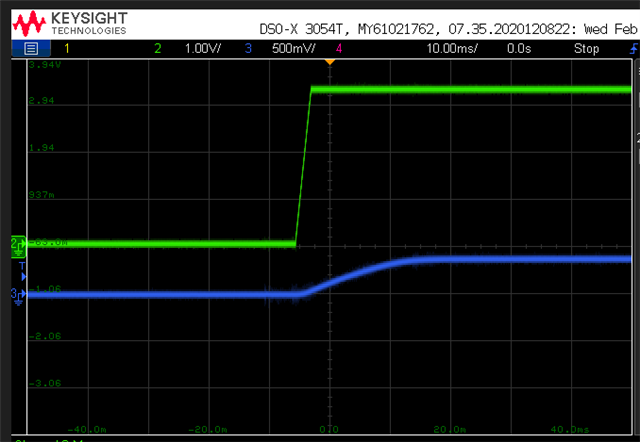

我们在测试的过程中发现当VDDOUT 上电后,会导致VDD有一个400mV的电压,波形如下:2通道是VDDOUT=3.3V,3通道是VDD;

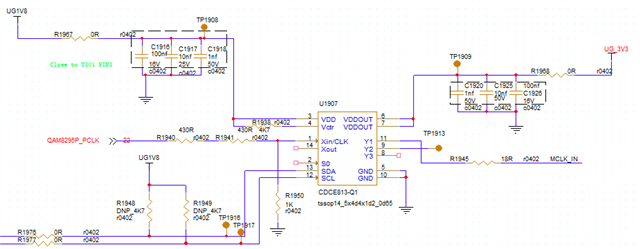

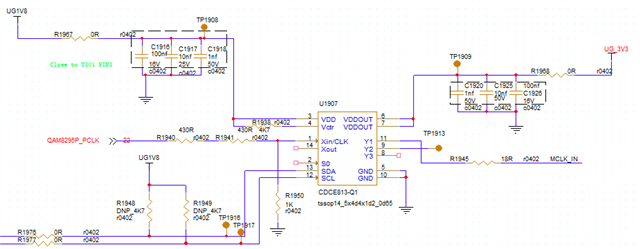

电路图如下:测试时断开R1967,R1941,R1956 R1976 R1977 91948 R1949 电阻

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: CDCE813-Q1

你好

我们在测试的过程中发现当VDDOUT 上电后,会导致VDD有一个400mV的电压,波形如下:2通道是VDDOUT=3.3V,3通道是VDD;

电路图如下:测试时断开R1967,R1941,R1956 R1976 R1977 91948 R1949 电阻

您好,

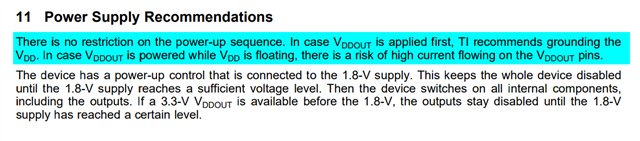

如下datasheet截图对芯片上电的建议:如果VDDOUT先上电,那么建议期间将VDD接地;如果在VDD浮动时给VDDOUT上电,那么VDDOUT引脚上会存在高电流流动的风险。

在您的测试中断开R1967,没有确切的电平加在VDD管脚,相当于VDD是浮动的,此时给VDDOUT上电,VDDOUT引脚上会流过高电流。

在您的电路中,UG1V8是通过UG_3V3产生的吗?如果是的话,那么在此过程中UG_3V3会对其产生电压UG1V8产生影响。另一个因素是,如果在一个回路中有突变信号,那么在其附近的线路中也会因线间或空间耦合而产生影响,这也是高频电路中时刻要注意的问题。这在VDDOUT引脚上有突变信号会对VDD产生影响是一样的道理。

amy

我又测试了一下 ,发现PIN 3 12 13 14 都会有电压输出 输出的幅值是相同的

宏伟

UG1V8是通过UG_3V3产生的吗? 不是的

我又测试了一下 ,发现PIN 3 12 13 14 都会有电压输出 输出的幅值是相同的

那么这应该是我说的线间或空间耦合因素产生的影响。

VDDOUT引脚上会流过高电流 ,会对813 造成哪些影响呢?

对813,我想主要的影响应该是其EMI性能,另一个是对VDDOUT管脚过流的影响,建议像10.2 Typical Application中串联磁珠。

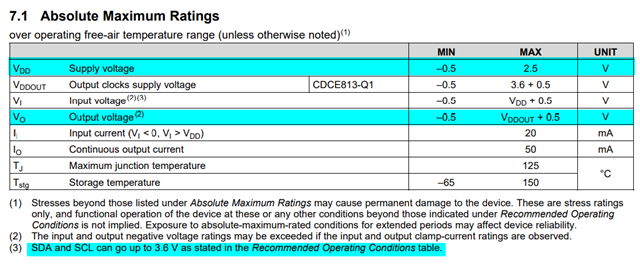

对其他管脚PIN 3 12 13 14应该没有影响,因为这些管脚都可以承受这个0.4V的电压:

3脚VDD是2.5V

12和13脚是3.6V

14脚是XOUT,可以到VDDOUT + 0.5

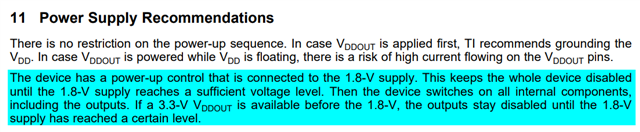

而且1.8V电源有通电控制装置,这使整个设备在VDD 1.8V电源达到足够的电压前 处于禁用状态。待VDD 1.8V上电后设备才使能所有内部组件,包括输出。即,如果3.3V VDDOUT在1.8V之前可用,则输出保持禁用状态,直到1.8V电源达到一定水平。

是否是ic本身的原因,还请帮忙查一下 感谢

您考虑的对,也可能是IC本身的原因,通过IC内部对其他管脚产生影响。

既然datasheet Power Supply Recommendations章节描述:There is no restriction on the power-up sequence. In case VDDOUT is applied first, TI recommends grounding the VDD.

我理解这寓意着可以先VDDOUT上电,不影响设备的工作,只不过VDDOUT先上电时,建议VDD接地,以避免VDDOUT大电流。