Part Number: CDCLVD1204

Other Parts Discussed in Thread: TMS320C6678

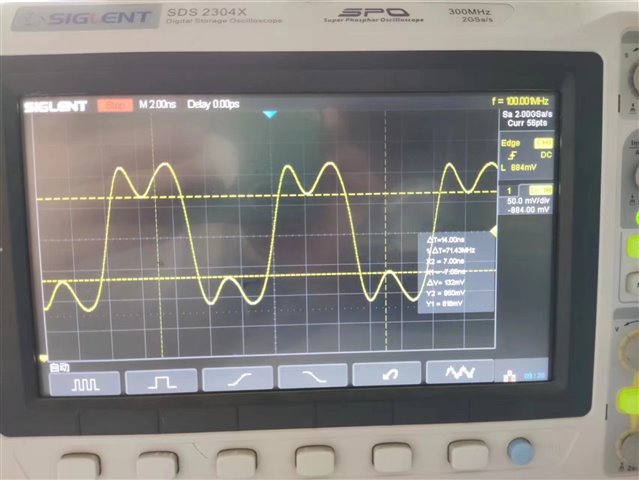

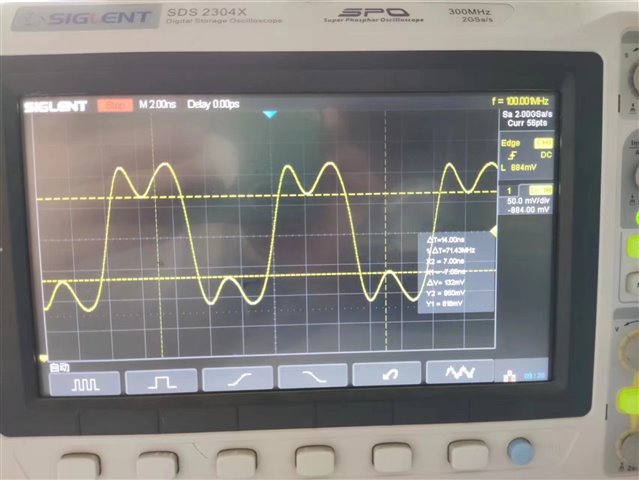

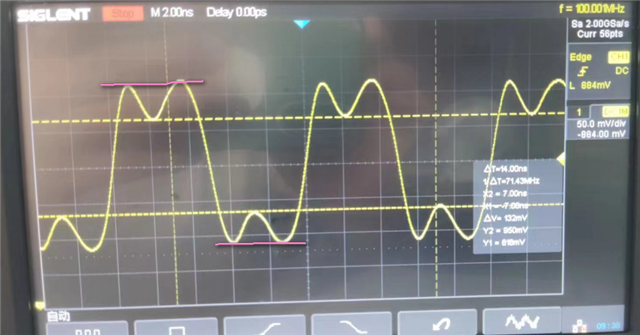

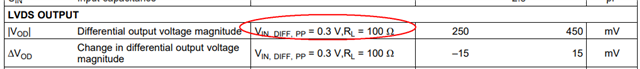

CDCLVD1204从手册P5看出Vpp为250-450mV,实际测试为200mV多点,测试结果见下图,

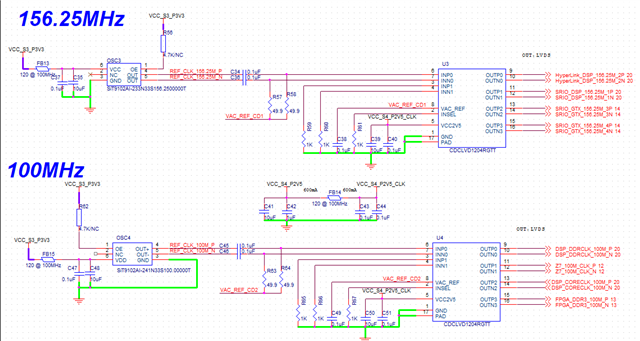

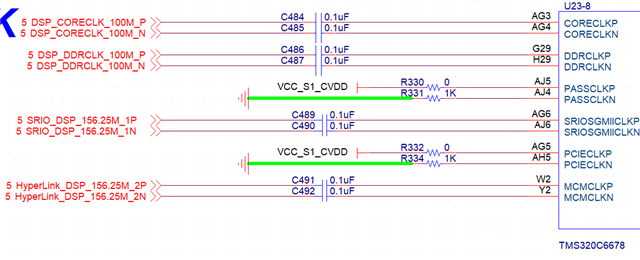

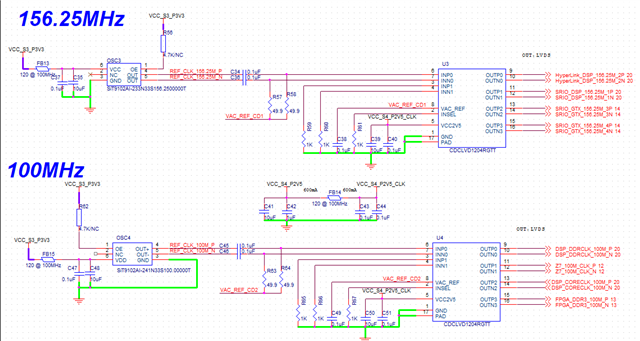

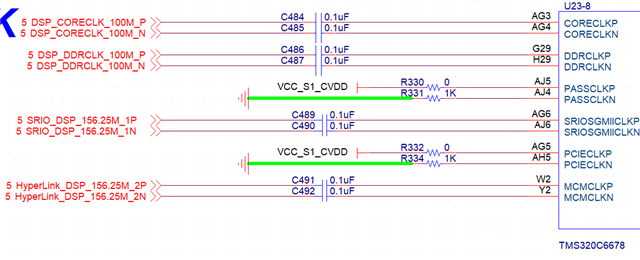

原理图见下:

问题:

1. 输出负载端是TMS320C6678,AC耦合,测量TMS320C6678 时钟P/N两端是114Ω,请问该设计有无问题?

2. 输出的幅值为何偏低?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: CDCLVD1204

Other Parts Discussed in Thread: TMS320C6678

CDCLVD1204从手册P5看出Vpp为250-450mV,实际测试为200mV多点,测试结果见下图,

原理图见下:

问题:

1. 输出负载端是TMS320C6678,AC耦合,测量TMS320C6678 时钟P/N两端是114Ω,请问该设计有无问题?

2. 输出的幅值为何偏低?

您好,根据您的波形,幅值测量应该是这里,peak to peak的值,您可以测试下这里的幅值是否满足datasheet中的要求。

波形出现了我们常说的回沟现象,很可能是阻抗不匹配导致的信号完整性问题。

C 6678的P/N 两端是114ohm,而CDCLVD1204的输出是100ohm,这样就会造成阻抗不连续。

抱歉没仔细看波形的参数,嗯看到回沟部分是132mV,峰峰值只有200mV。

那么156.25Mhz输入是否满足输入要求, 1.25V共模电压,0.3Vpp~1.6Vpp范围?

250mV~450mV的幅值是在端接之后得到的幅值。

您是如何测试的?看波形您是测试了差分输出端的单端,那么需要单端端接50ohm负载测量。

如果是使用差分碳棒,那么需要在OUT+和OUT-之间端接100ohm电阻然后再进行测量。