Part Number: LMK5B12204

使用IIC 将导出的寄存器配置文件写入后

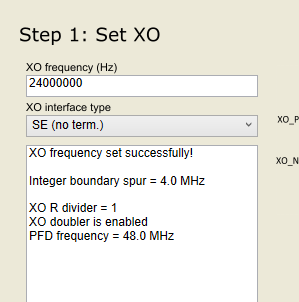

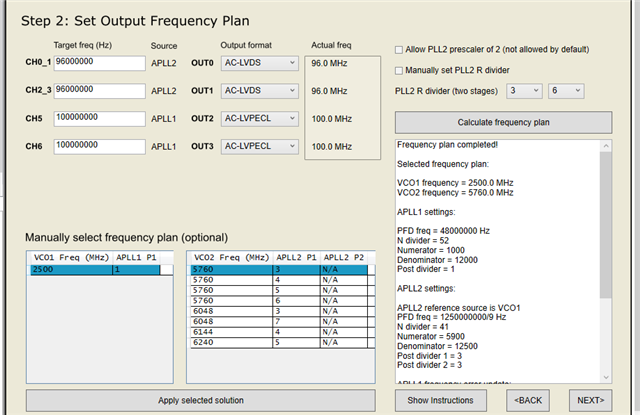

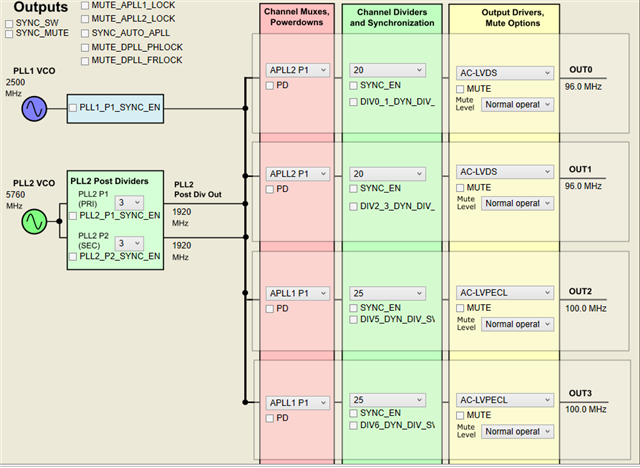

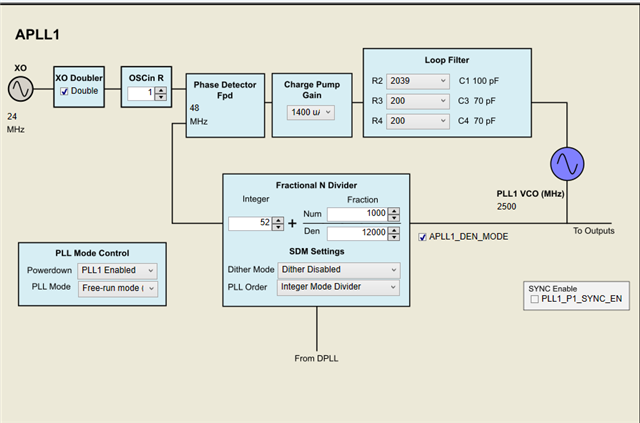

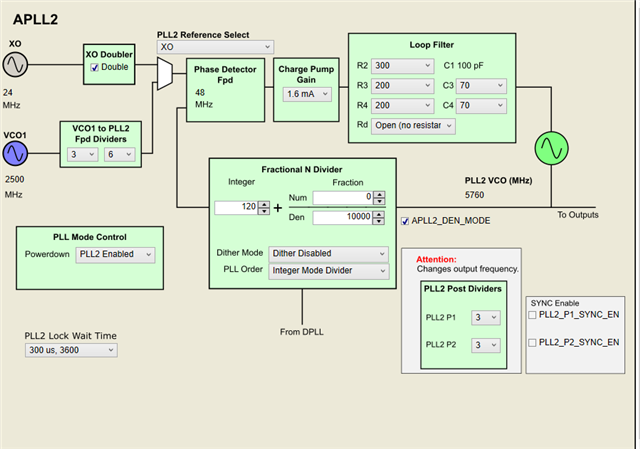

使用24M TCXO(频偏不大于1ppm)作为输入,APLL1用来产生100M,APLL2用来产生96M,禁止DPLL,两个APLL都是Free-run模式。出现以下问题:

1 只要使用APLL1输出,不管多少输出频率,输出时钟jitter抖很好,但是存在频偏,100M能偏移到99.917M;

2 只要使用APLL2输出,输出时钟的抖动非常大-35dBc @100k,且存在很大频偏,时漂2分钟能飘400k。

另外通过status0确认过PLL有lock。

具体配置如下:LMK5B12204.tcs