LMK04832在只用PLL2是输出无杂散,在使用PLL1后输出在8K处存在杂散。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好,如果参考时钟或者电源路径上有低于环路带宽的杂散,那么是不会随着PLL的行为变化而变化的。

根据您的描述,PLL2无杂散,PLL1有杂散,那么因为环路带宽的变化而变化的杂散可能会由于VCC_VCO、VCC_PLL1或 VCC_CP 这几处引入的,还会有可能耦合到环路滤波器,调制VCO的电压。另外,输出在8K处存在杂散,还有可能是因为附近输出在不同频率下相互作用产生的串扰杂散。如果频率不同的输出彼此相邻或相连,这可能会导致输出之间产生电容或电感耦合,从而表现为串扰。

所以我想可能先从这几处地方排查下,VCC_VCO、VCC_PLL1或 VCC_CP 的电源处是否引入杂散,输出是否由于串扰导致杂散。

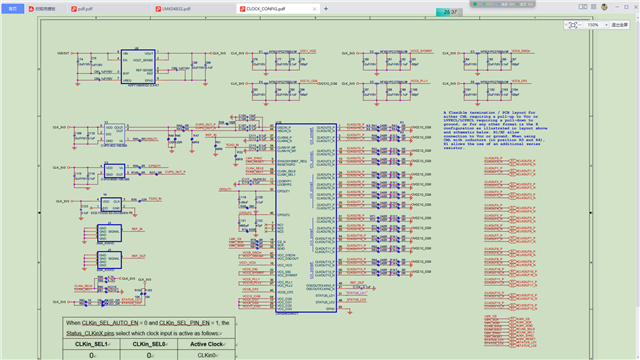

非常感谢您的回复。我们目前在硬件上调节了环路滤波器。但是效果不是太明显,应该还是没有找到原因。同时我们这边在配置寄存器上是否还有问题。目前使用FPGA操作SPI向LMK04832中配置寄存器。使用了TICS PRO生成的配置。我们CLKIN0处使用了外部参考100mhz(通过信号源发进来)。同时我们使用CLK1处使用了内部100mhz的贴片晶振输入。OSIN使用了100mhz的晶振输入。在TICS PRO上生成寄存器。使用FPGA向内部配置进去。同时寄存器15F写入0B,寄存器16E写入13。使用STATUS_LD1,STATUS_LD2返回PLL锁定状态。很可惜。我们只看到了STATUS_LD2返回了一个高电平。您能帮我们看一下这个寄存器配还有什么问题吗?如果方便的话能否帮我们生成一个txt。万分感谢。我下方附上我们的寄存器配置文件以及电路。

R0 (INIT) 0x000090 R0 0x000000 R2 0x000220 R3 0x000306 R4 0x000463 R5 0x0005D1 R6 0x000670 R12 0x000C51 R13 0x000D04 R256 0x010019 R257 0x01010A R258 0x010200 R259 0x010305 R260 0x010420 R261 0x010500 R262 0x010606 R263 0x010754 R264 0x01080A R265 0x01090A R266 0x010A00 R267 0x010B05 R268 0x010C20 R269 0x010D00 R270 0x010E00 R271 0x010F51 R272 0x011014 R273 0x01110A R274 0x011200 R275 0x011305 R276 0x011420 R277 0x011500 R278 0x011601 R279 0x011755 R280 0x01180A R281 0x01190A R282 0x011A00 R283 0x011B05 R284 0x011C00 R285 0x011D00 R286 0x011E01 R287 0x011F55 R288 0x012014 R289 0x01210A R290 0x012200 R291 0x012305 R292 0x012400 R293 0x012500 R294 0x012601 R295 0x012755 R296 0x012814 R297 0x01290A R298 0x012A00 R299 0x012B05 R300 0x012C00 R301 0x012D00 R302 0x012E01 R303 0x012F55 R304 0x01300E R305 0x01310A R306 0x013200 R307 0x013305 R308 0x013410 R309 0x013500 R310 0x013601 R311 0x013744 R312 0x013824 R313 0x013903 R314 0x013A00 R315 0x013BC8 R316 0x013C00 R317 0x013D08 R318 0x013E03 R319 0x013F00 R320 0x014000 R321 0x014100 R322 0x014200 R323 0x014310 R324 0x0144FF R325 0x014500 R326 0x014618 R327 0x01471A R328 0x014805 R329 0x014905 R330 0x014A00 R331 0x014B02 R332 0x014C00 R333 0x014D00 R334 0x014EC0 R335 0x014F7F R336 0x015001 R337 0x015101 R338 0x015200 R339 0x015300 R340 0x015405 R341 0x015500 R342 0x015604 R343 0x015700 R344 0x015864 R345 0x015900 R346 0x015A04 R347 0x015BC0 R348 0x015C20 R349 0x015D00 R350 0x015E1E R351 0x015F0B R352 0x016000 R353 0x016104 R354 0x0162AC R355 0x016300 R356 0x016400 R357 0x016519 R361 0x016958 R362 0x016A20 R363 0x016B00 R364 0x016C00 R365 0x016D00 R366 0x016E13 R371 0x017310 R375 0x017700 R386 0x018200 R387 0x018300 R358 0x016600 R359 0x016700 R360 0x016819 R1365 0x055500

我们CLKIN0处使用了外部参考100mhz(通过信号源发进来)。同时我们使用CLK1处使用了内部100mhz的贴片晶振输入。OSIN使用了100mhz的晶振输入。在TICS PRO上生成寄存器。使用FPGA向内部配置进去。同时寄存器15F写入0B,寄存器16E写入13。使用STATUS_LD1,STATUS_LD2返回PLL锁定状态。很可惜。我们只看到了STATUS_LD2返回了一个高电平

您好,输出频率是多少?

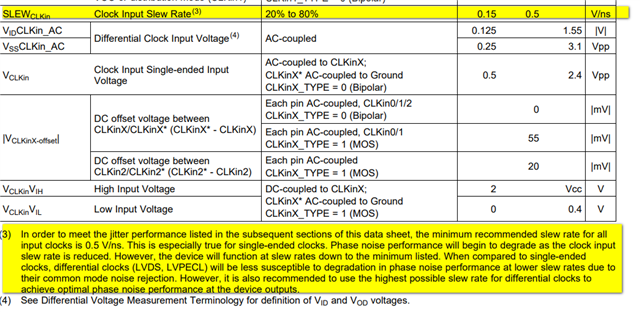

另外,您这里提到STATUS_LD1没有lock,而CLKIN0是外部参考时钟输入,我看了下数据手册,外部惨参考时钟输入有slew rate的要求,您要确认下输入是否满足0.15V/ns~0.5V /ns的要求?

我们使用外部信号源输入是满足要求的,CLKin1是晶振进来的100mhz,clkin0是外部信号源进来的100mhz。我选择输入为clkin0,或者选择输入为clkin1。这里的STATUS_LD1都没有lock(拉高)。我们继续尝试调整了环路滤波器,选择clkin0外部信号源输入100mhz信号,在寄存器配置中将phase detector polarity调整为positive,以及charge pump gain调整为1550ua,目前输出时钟稳定。

但是STATUS_LD1依旧没有lock(拉高)。这里还有什么需要注意的地方吗?

当PLL1失锁时,用示波器同时监测CPOUT1的电压状况看是如何变化的。

第二,我认为您的思路从环路滤波器考虑是正确的,我建议使用滤波器设计软件PLLatinumSim去check相位裕度是否达到45度。

https://www.ti.com/tool/PLLATINUMSIM-SW?keyMatch=PLLATINUMSIM