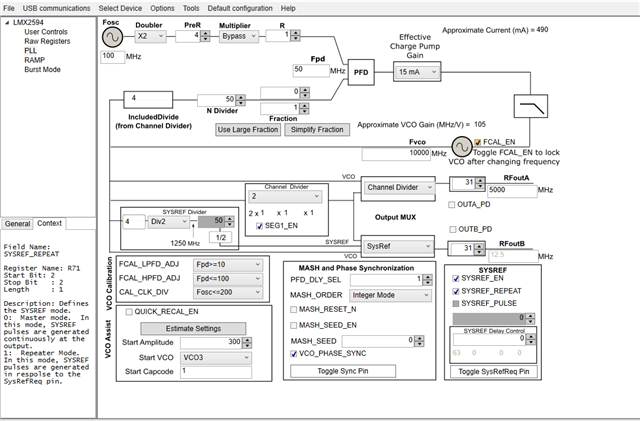

Part Number: LMX2594

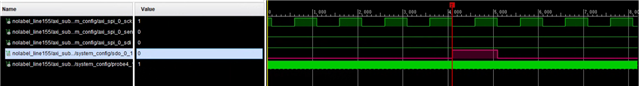

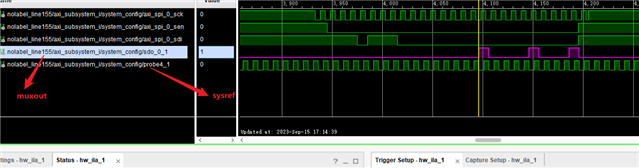

配置寄存器后r110[10:9]始终为11,请帮忙看看配置哪里有问题,三种vco assist方式都试过,输入oscin为100M,产生一路5000M时钟和一路12.5M sysref

寄存器配置如下:

R112 0x700000

R111 0x6F0000

R110 0x6E0400

R109 0x6D0000

R108 0x6C0000

R107 0x6B0000

///read back register

R106 0x6A0000

R105 0x690021

R104 0x680000

R103 0x670000

R102 0x660000

R101 0x650011

R100 0x640000

R99 0x630000

R98 0x620000

R97 0x610888

R96 0x600000

R95 0x5F0000

R94 0x5E0000

R93 0x5D0000

R92 0x5C0000

R91 0x5B0000

R90 0x5A0000

R89 0x590000

R88 0x580000

R87 0x570000

R86 0x560000

R85 0x550000

R84 0x540000

R83 0x530000

R82 0x520000

R81 0x510000

R80 0x500000

R79 0x4F0000

////ramping function

R78 0x4E016F //ramp_thresh = 0;quick_recal_en = 0 for NO ASSIST/PARTIAL ASSIST/FULL ASSIST;=1 for CLOSE FREQUENCY ASSIST; VCO_CAPCTRL_STRT越小生成的vco core带宽越高,此处设为183(NO ASSIST)

R77 0x4D0000 //固定值

R76 0x4C000C //固定值

R75 0x4B0800 //CHDIV=2

R74 0x4A0000 //SYSREF_PULSE_CNT、JESD_DAC4_CTRL、JESD_DAC3_CTRL,均设为0

R73 0x49003F //JESD_DAC2_CTRL、JESD_DAC1_CTRL,上面四个值加起来要=63,此处设JESD_DAC1_CTRL=63

R72 0x480017 //SYSREF_DIV=50

R71 0x47004D //SYSREF_DIV_PRE=2,SYSREF_PULSE=0,SYSREF_EN =1,SYSREF_REPEAT=1

R70 0x460000 //If the designer does not use this device in fractional mode with VCO_PHASE_SYNC = 1, then this field can be set to 0.------------------------待考虑

R69 0x450000 //同R70

R68 0x4403E8 //固定值

R67 0x430000 //固定值

R66 0x4201F4 //固定值

R65 0x410000 //固定值

R64 0x401388 //固定值

R63 0x3F0000 //固定值

R62 0x3E0322 //固定值

R61 0x3D00A8 //固定值

R60 0x3C0000 //VCO校准成功和lock detect拉高之间的延迟值,延迟值为pd的周期数?(The delay added is in phase-detectorcycles.),设为0表明校准成功之后立即拉高,此处设为0

R59 0x3B0001 //LD_TYPE--lock detect type,有两种类型:0 = VCO Calibration Status;1 = Indirect Vtune 如果为0,且muxout设置为lock detect时,只有在vco校准完成并且ld_dly也延迟完之后才会拉高;如果为1,锁定后,要么muxout拉高,要么回读为2(即锁定),此处设为1合适。

R58 0x3A3001 //INPIN_IGNORE=0(sync sysrefreq pin is used),INPIN_HYST=0(used for lvds),INPIN_LVL=3(used for lvds),INPIN_FMT=0(0: SYNC = SysRefReq = CMOS)

R57 0x390020 //固定值

R56 0x380000 //固定值

R55 0x370000 //固定值

R54 0x360000 //固定值

R53 0x350000 //固定值

R52 0x340820 //固定值

R51 0x330080 //固定值

R50 0x320000 //固定值

R49 0x314180 //固定值

R48 0x300300 //固定值

R47 0x2F0300 //固定值

R46 0x2E07FE //OUTB_MUX= 2,SYSREF

R45 0x2DC0DF //OUTA_MUX =0,Channel divider OUT_ISET=0,Maximum output power boost OUTB_PWR=31

R44 0x2C1F00 //OUTA_PWR=31 OUTB_PD=0,OUTA_PD=0 MASH_RESET_N=0,All fractions are ignored MASH_RESET_N=1,分数模式使能 MASH_ORDER=0,Integer mode;

R43 0x2B0000 //PLL_NUM[15:0] = 0

R42 0x2A0000 //PLL_NUM[31:16] = 0

R41 0x290000 //MASH_SEED[15:0] = 0

R40 0x280000 //MASH_SEED[31:16] = 0

R39 0x270001 //PLL_DEN[15:0] = 1

R38 0x260000 //PLL_DEN[15:0] = 0

R37 0x250104 //MASH_SEED_EN = 0 PFD_DLY_SEL 根据table2来进行选择,此处=1

R36 0x240032 //PLL_N[15:0]

R35 0x230004 //固定值

R34 0x220000 //PLL_N[2:0]

R33 0x211E21 //固定值

R32 0x200393 //固定值

R31 0x1F43EC //CHDIV_DIV2=1 必须enable吗?

R30 0x1E318C //固定值

R29 0x1D318C //固定值

R28 0x1C0488 //固定值

R27 0x1B0002 //固定值

R26 0x1A0DB0 //固定值

R25 0x190C2B //固定值

R24 0x18071A //固定值

R23 0x17007C //固定值

R22 0x160001 //固定值

R21 0x150401 //固定值

R20 0x14F848 //根据辅助模式的不同来选择,此处先选择NO ASSIST模式,则VCO_SEL_FORCE = 0,VCO_SEL = 7 ,VCO_DACISET_STRT = 300 and VCO_CAPCTRL_STRT = 183

R19 0x1327B7 //VCO_CAPCTRL= 183 ,This sets the final amplitude for the VCO calibration in the case that amplitude calibration is forced.

R18 0x120064 //固定值

R17 0x11012C //VCO_DACISET_STRT=300

R16 0x100080 //VCO_DACISET = 128,不是force模式下,这个值无所谓

R15 0x0F064F //固定值

R14 0x0E1E70 //Charge Pump = 15mA

R13 0x0D4000 //固定值

R12 0x0C5002 //PLL_R_PRE =2

R11 0x0B0028 //PLL_R = 2

R10 0x0A10D8 //MULT=BYPASS

R9 0x091604 //DOUBLER ENABLED

R8 0x082000 //VCO_DACISET_FORCE = 0;VCO_CAPCTRL_FORCE = 0(NO ASSIST)

R7 0x0740B2 //out_force = 0,Works with OUT_MUTE in disabling outputs when VCO calibrating.

R6 0x06C802 //固定值

R5 0x0500C8 //固定值

R4 0x041943 //ACAL_CMP_DLY = 25

R3 0x030642 //固定值

R2 0x020500 //固定值

R1 0x010808 //CAL_CLK_DIV=0

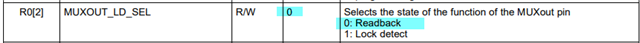

R0 0x006610 //RAMP_EN =0 VCO_PHASE_SYNC =1 OUT_MUTE = 1 FCAL_HPFD_ADJ =0 FCAL_LPFD_ADJ=0 FCAL_EN=0后需再翻转为1 muxout_ld_sel=0,readback reset=0(normal) powerdown=0(normal)

sleep(10ms)

R0 0x6618