Other Parts Discussed in Thread: LMK04828, LMK04832

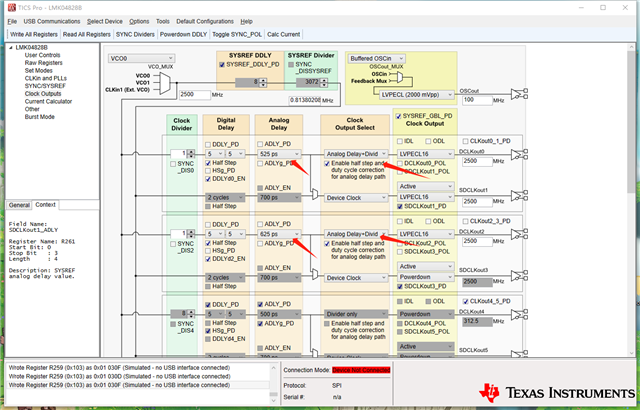

各位专家。我这边正在验证lmk04828的数字延迟和模拟延迟。输入为clkin1输入20mhz时钟,oscin输入为100mhz时钟。vco0为2500mhz。

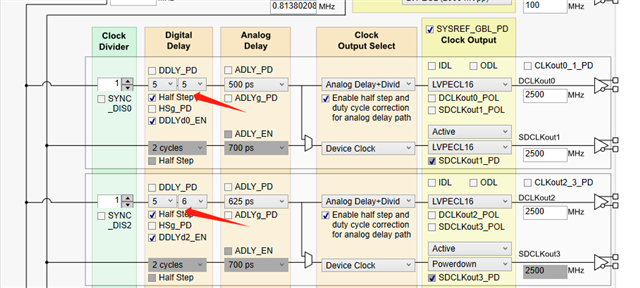

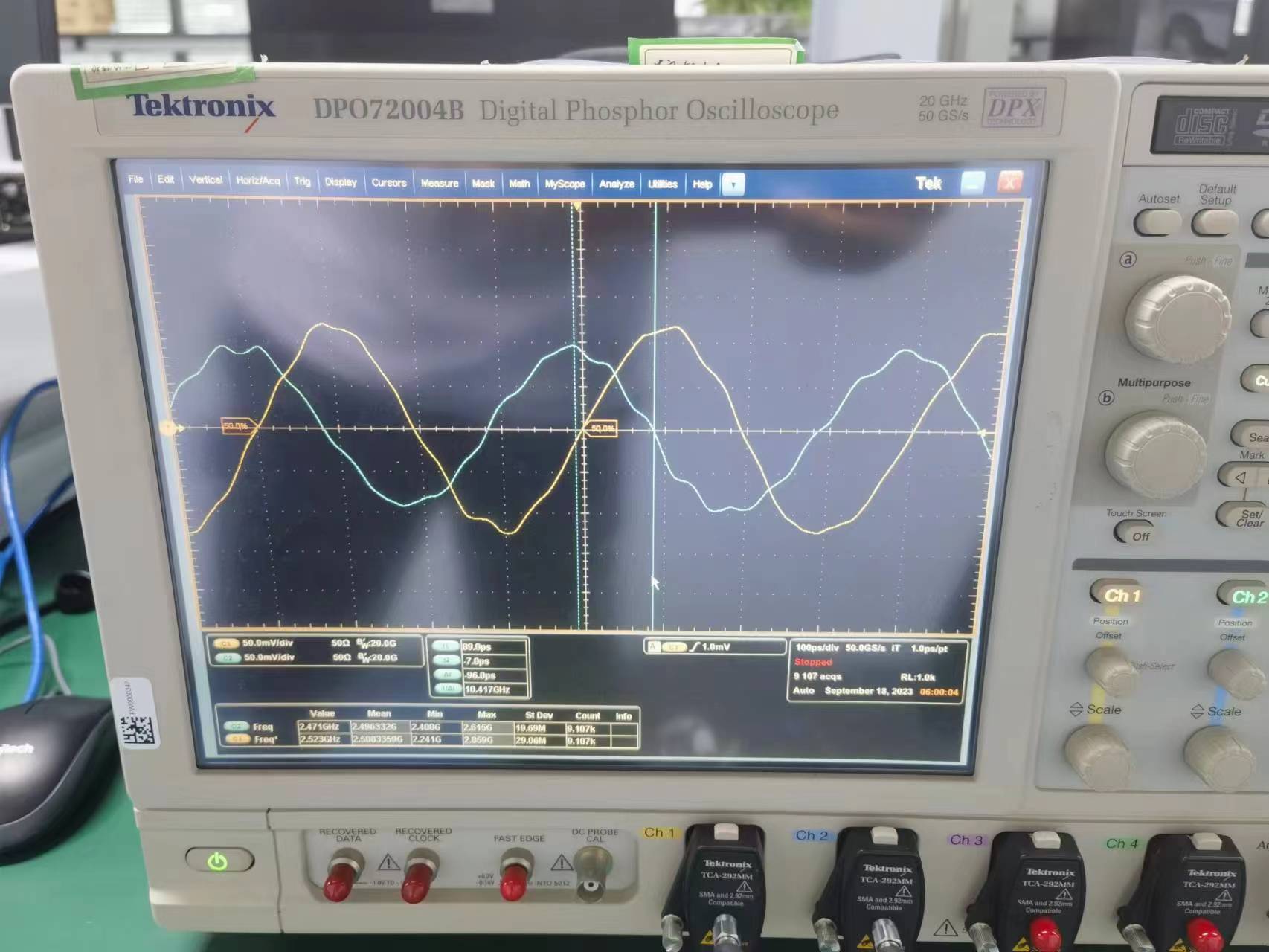

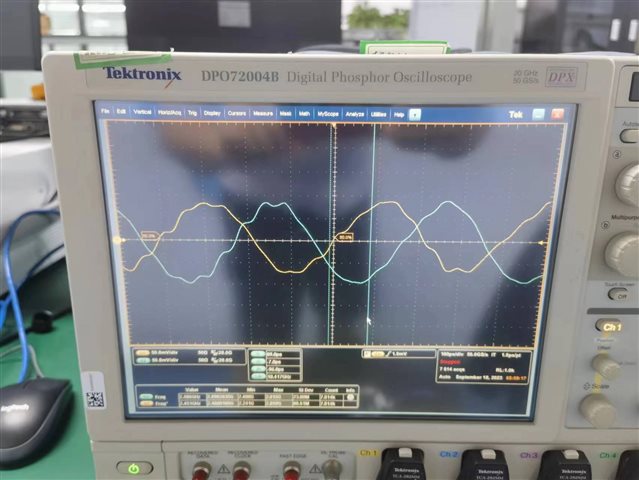

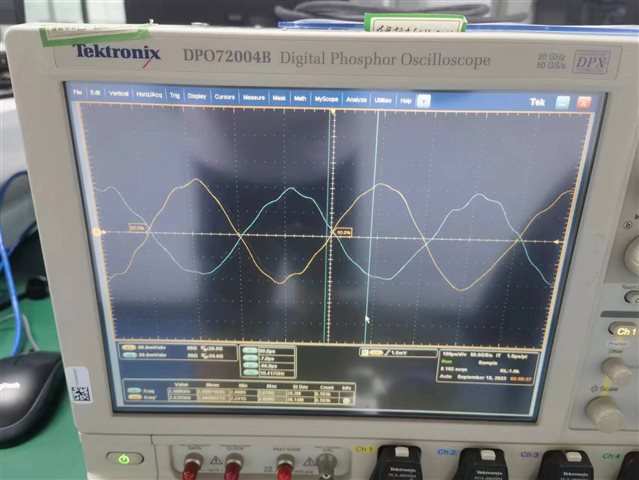

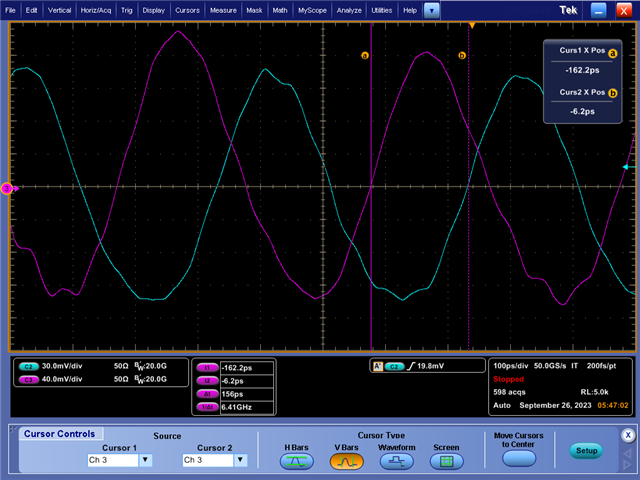

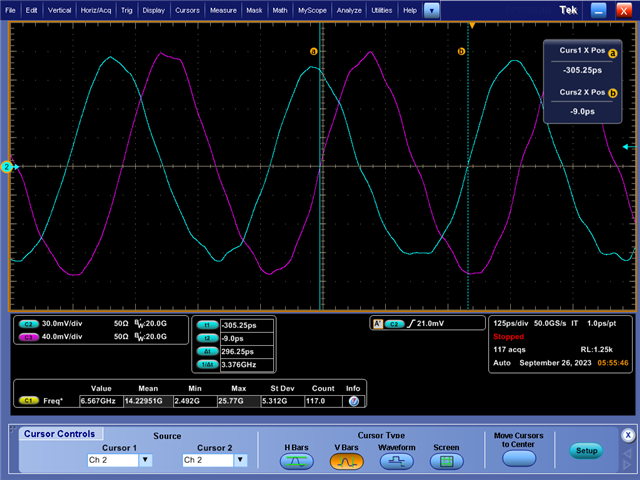

dclkout0为2500mhz,dclkout2为2500mhz。我使用示波器测试这两个时钟的延迟。

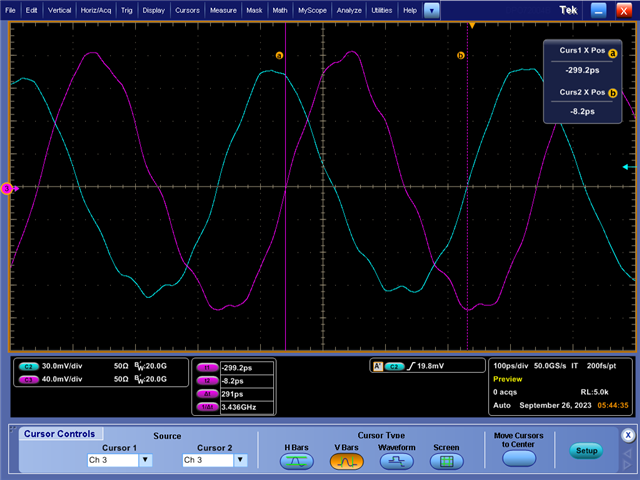

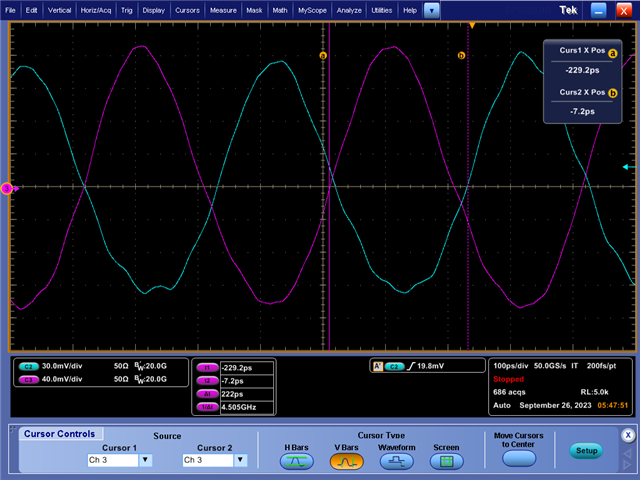

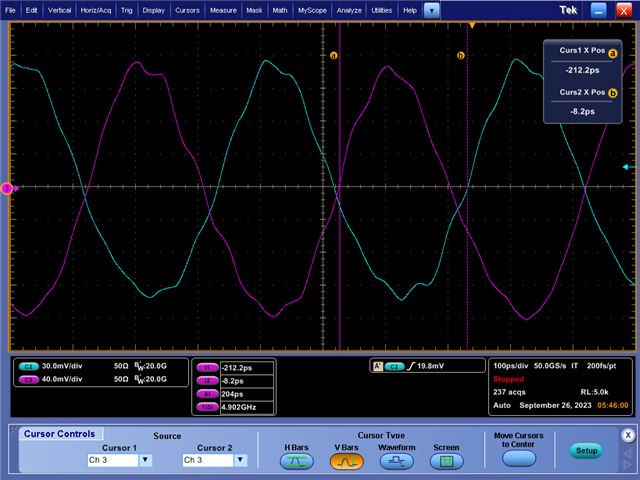

关于模拟延迟。我在TICSPRO上设置clock output select设置为analog delay + divider。在芯片配置完成后。更改analog delay中的延迟值。发现时钟延迟更改了。但是改动的值和我设置的不太一样。关于模拟延迟这边操作有什么问题吗?

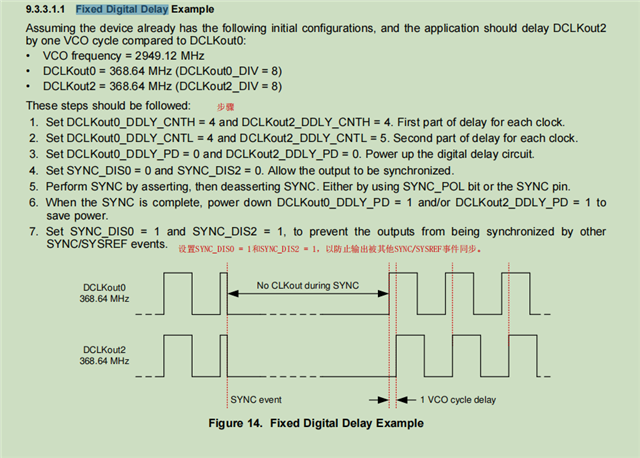

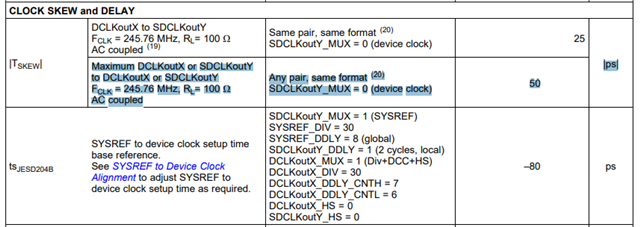

另外我准备测试数字延迟功能。数字延迟按照手册上说拥有两个模式。

我准备验证Fixed Digital Delay。使用手册上说明的例子。

设置DCLKout0_DDLY_CNTH/L的值为4,4。设置DCLKout0_DDLY_CNTH/L的值为4,5;

设置DCLKout0_DDLY_PD = 0 and DCLKout2_DDLY_PD = 0;

设置SYNC_DIS0 = 0 and SYNC_DIS2 = 0;

在操作sync_pol写1在写0。

已知VCO0为2500mhz。我修改后延迟为半个VCO0周期应该为200ps。即dclkout0和dclkout1应该反相。但是事实是,输出时钟毫无变化。我这边的操作还有什么漏掉的地方吗?