Other Parts Discussed in Thread: PLLATINUMSIM-SW

大家好:

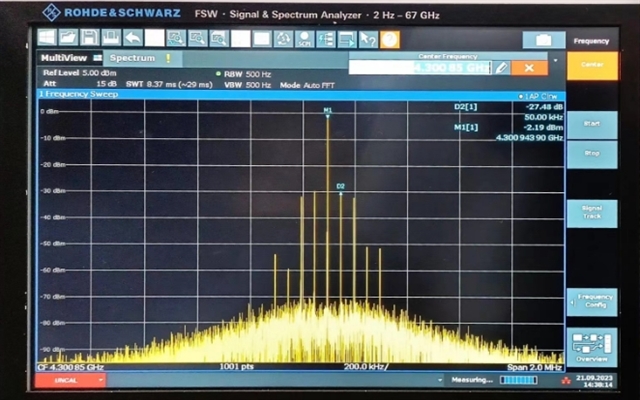

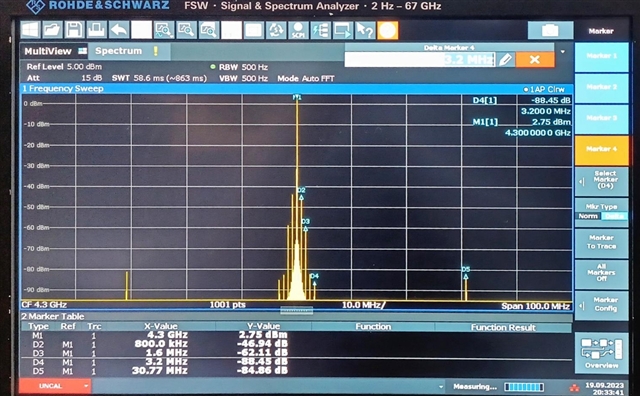

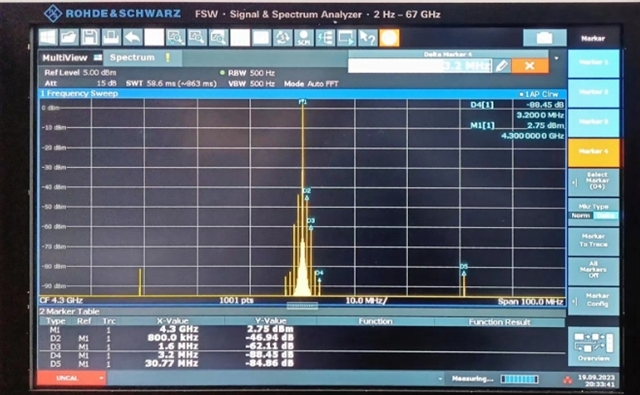

在使用LMX2694-EP芯片输出信号时,测试500-6000M频段输出是,发现部分频段信号近端有杂散,比如在4300MHz时,杂散离主信号最近;

查了些资料,好像是PLL的整数边界杂散(IBS, Integer Boundary Spurs),即鉴相频率及其谐波和输出信号杂散,如112.88*35-4300=0.8M;

减小电荷泵电流可以减小点杂散,但不够,希望可以抑制到70dBc以下;

按照上述计算,最大的杂散应该在122.88*n附近;

请问有什么好的解决办法吗?

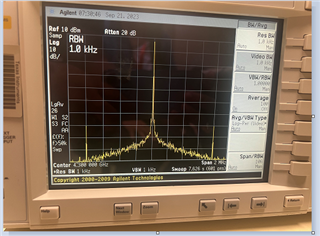

下图是输出4300M信号频谱:

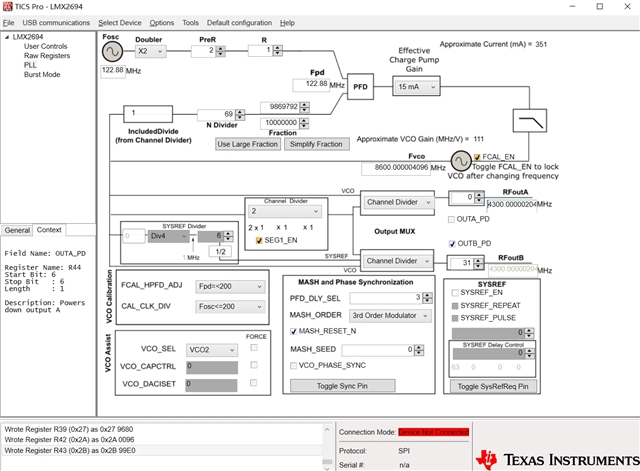

下图为4300M时的配置: