Part Number: LMK04828

Other Parts Discussed in Thread: ADC12QJ1600, ADC12QJ1600EVM

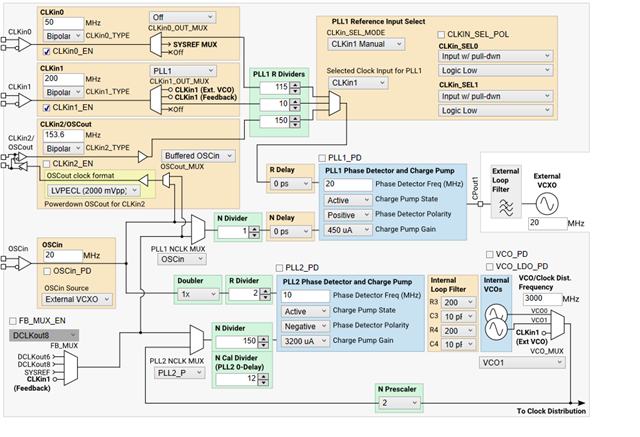

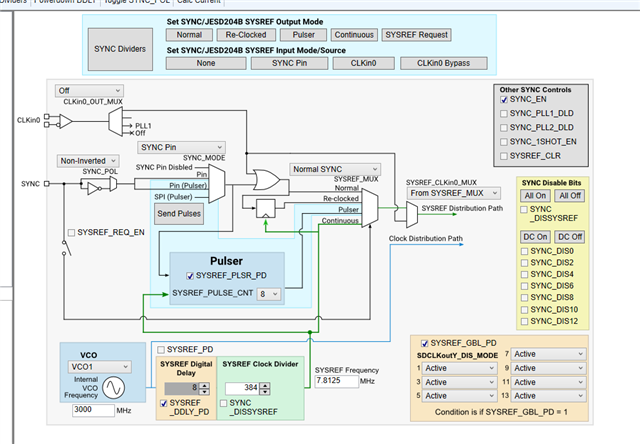

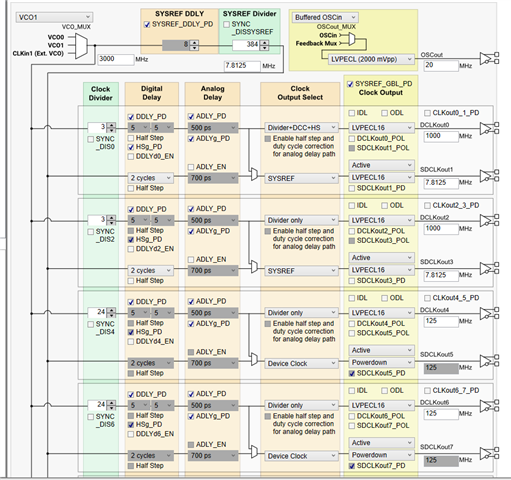

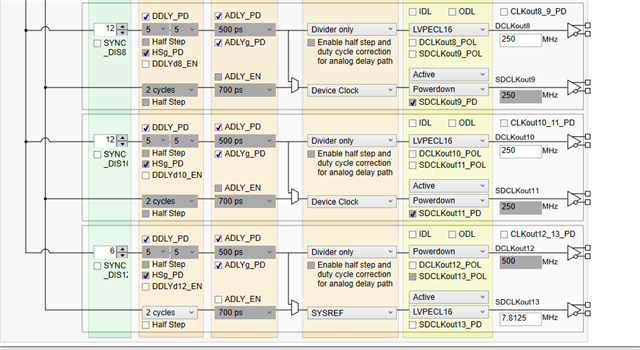

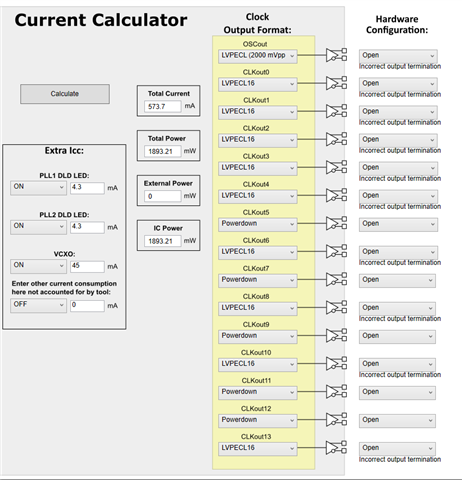

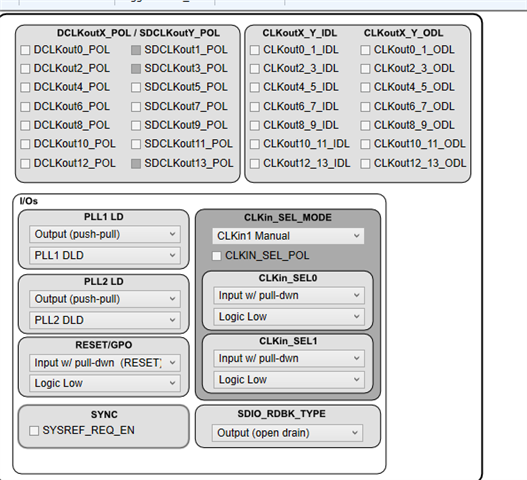

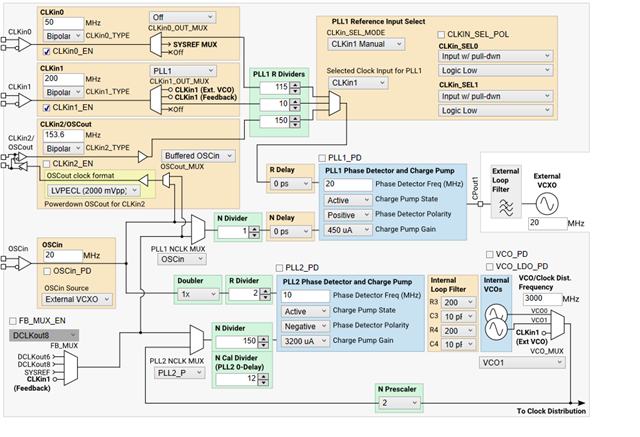

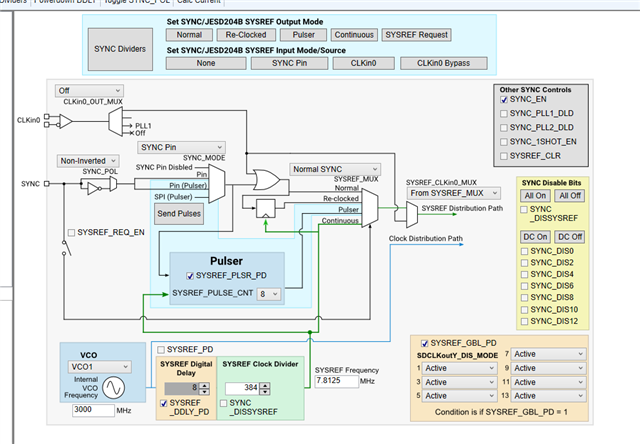

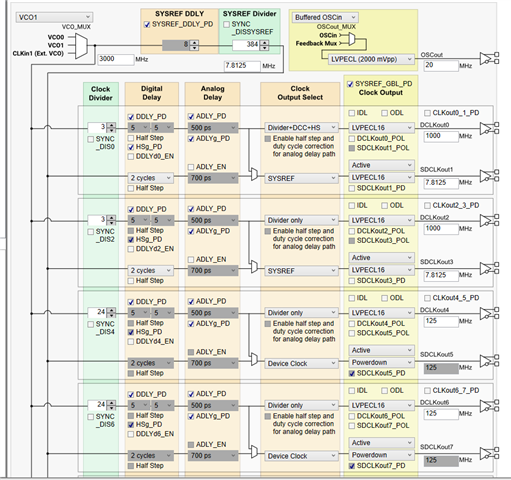

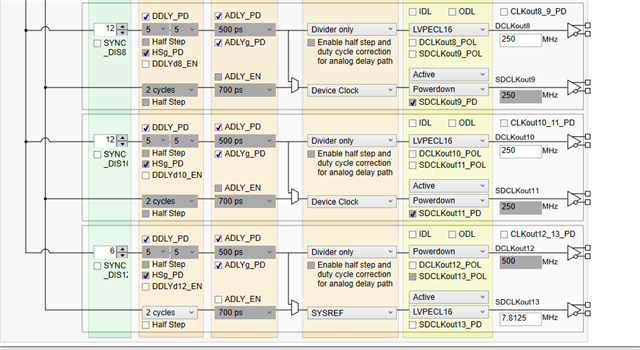

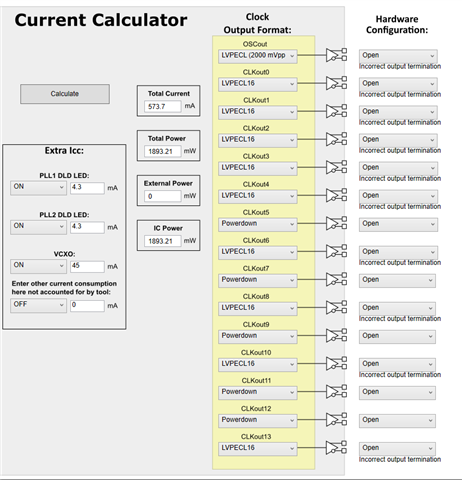

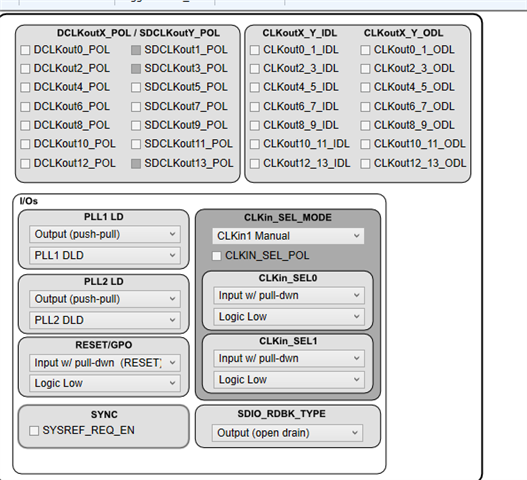

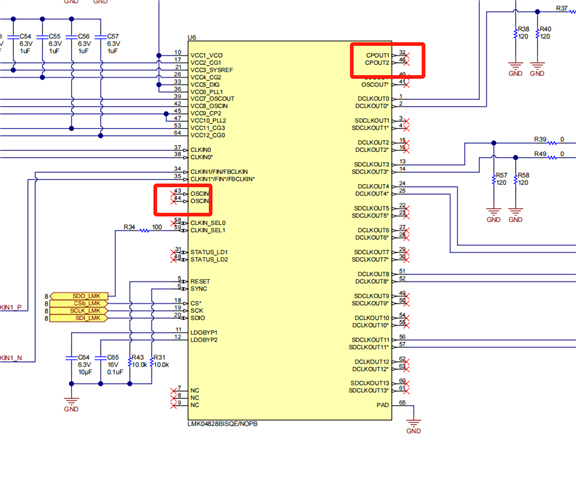

ticspro的设计如下图所示,请问我这个配置有问题吗?如果有的话我需要怎么修改呢

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: LMK04828

Other Parts Discussed in Thread: ADC12QJ1600, ADC12QJ1600EVM

ticspro的设计如下图所示,请问我这个配置有问题吗?如果有的话我需要怎么修改呢

您好,我用TICSpro试了下,根据您的输入输出得到的配置是相同的。

你是根据Status_LD1和Status_LD2 来判断的PLL是否lock了是吗?

抱歉我这么晚回复您,是这样的,我们硬件之前的设计是按照ADC12QJ1600的电路图设计的,如下图,这上面红框框柱的CPout和OSCIN组成的反馈回路中并没有链接压控晶振和滤波器,导致pll1的反馈回路无法建立,并且pll2没有输入,导致这两个PLL均无法锁定。

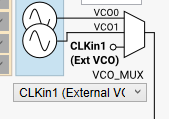

现在我的解决方案是在CLKIN1的接口中接入一个500M的频率,然后再VCOMUX中使用EXT VCO,直接将这个500M的时钟跳过两个锁相环,直接进行分频来得出需要的频率,这个使用方式应当也符合ADC12QJ1600EVM的使用方式。

您好,感谢您的反馈,那是说目前没有问题了是吗?

如果暂时没有问题的话, 我就先把这个帖子关掉了,后续有什么问题再讨论。