Part Number: LMK5B12204

我在使用LMK5B12204的时候,发现在禁用DPLL,APLL1和APLL2独立运行(都使用XO输入时钟)时,APLL2无论如何也锁定不了的情况,这也导致了APLL2最后输出的时钟与我想要的时钟存在频偏,且抖动很大,APLL1是正常的,且能从status中看到BAW和APLL1的lock

附上我的TICSPRO文件tmp1.tcs

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: LMK5B12204

我在使用LMK5B12204的时候,发现在禁用DPLL,APLL1和APLL2独立运行(都使用XO输入时钟)时,APLL2无论如何也锁定不了的情况,这也导致了APLL2最后输出的时钟与我想要的时钟存在频偏,且抖动很大,APLL1是正常的,且能从status中看到BAW和APLL1的lock

附上我的TICSPRO文件tmp1.tcs

您好,APLL2也是使用的XO作为输入,还是使用APLL1经过分频后作为输入?

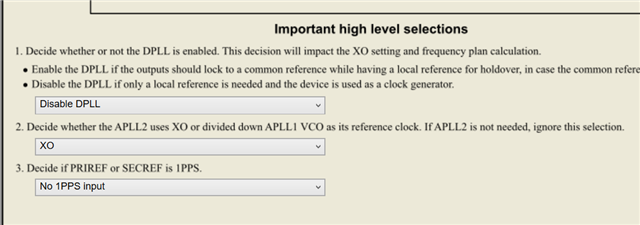

TICSPro起初这里的是否有设定?第一步disable DPLL,然后APLL2输入选择XO还是APLL1分频后作为输入。第三,PRIREF和SECREF是否有输入。

另外,XO输入频率是多少,输出哪几个通道,输出频率为多少?我这边使用TICSpro配置下。

同时我观察到您给出的页面中CH2_3的值是5MHz(少打一个0),但我不确定是否是这个原因导致的error

是的,我这里少打了一个0,然后就不会报这个错误了。

我看了下您每个页面的配置和分频系数都是没问题的。

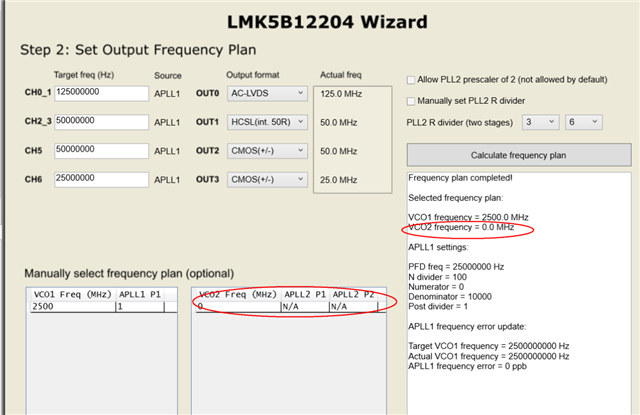

但是我认为APLL2无法锁定的原因应该在这里,VCO2的频率为0,事实上VCO2=5500Mhz。并且这里APLL2_P1显示NA状态。

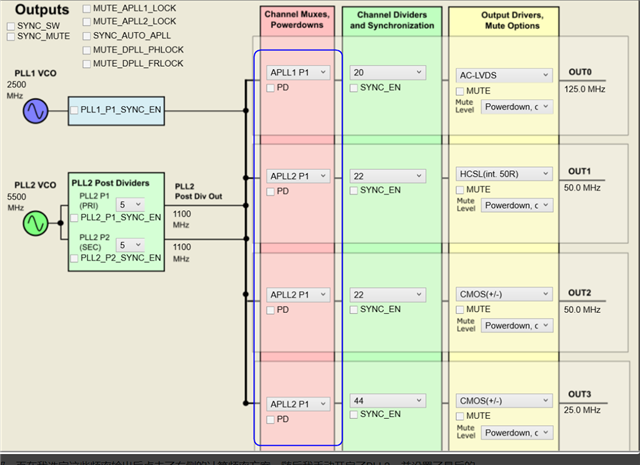

但是我看在outputs这里已经选择了输出源APLL2_P1.也就是这几个寄存器的值。

R54(0x36)=0x00 36D8

R59(0x3B)=0x00 3BD8

R61(0x3D)=0x00 3DD8

附件是我使用TICSPro导出的寄存器,您试试看是否有输出。

R0 0x000010 R1 0x00010B R2 0x000235 R3 0x000332 R4 0x000404 R5 0x00050E R6 0x000617 R7 0x00078E R8 0x000802 R10 0x000AC8 R11 0x000B00 R12 0x000C03 R13 0x000D08 R14 0x000E00 R15 0x000F00 R16 0x001000 R17 0x00111D R18 0x0012FF R19 0x001308 R20 0x001420 R21 0x001501 R22 0x001600 R23 0x001755 R24 0x001855 R25 0x001900 R26 0x001A00 R27 0x001B00 R28 0x001C01 R29 0x001D00 R30 0x001E40 R32 0x002044 R35 0x002300 R36 0x002403 R37 0x002500 R38 0x002600 R39 0x002703 R40 0x002803 R41 0x002900 R42 0x002A11 R43 0x002BC2 R44 0x002C00 R45 0x002D03 R46 0x002E11 R47 0x002F87 R48 0x003050 R49 0x00314A R50 0x003200 R51 0x003318 R52 0x003418 R53 0x003513 R54 0x0036D8 R55 0x003718 R56 0x003815 R57 0x003918 R58 0x003A0F R59 0x003BD8 R60 0x003C14 R61 0x003DD8 R62 0x003E2B R63 0x003F18 R64 0x004000 R65 0x004100 R66 0x004200 R67 0x004318 R68 0x004408 R69 0x004500 R70 0x004603 R71 0x004700 R72 0x004833 R73 0x004900 R74 0x004A00 R75 0x004B00 R76 0x004C00 R77 0x004D0F R78 0x004E00 R79 0x004F01 R80 0x005080 R81 0x00510A R82 0x005200 R83 0x00530E R84 0x005410 R85 0x00555D R86 0x005600 R87 0x00571E R88 0x005884 R89 0x005982 R90 0x005A00 R91 0x005B14 R92 0x005C00 R93 0x005D0E R94 0x005E10 R95 0x005F5D R96 0x006000 R97 0x00611E R98 0x006284 R99 0x006382 R100 0x006430 R101 0x006501 R102 0x006644 R103 0x00670F R104 0x00681F R105 0x006905 R106 0x006A00 R107 0x006B64 R108 0x006C00 R109 0x006D32 R110 0x006E00 R111 0x006F00 R112 0x007000 R113 0x007127 R114 0x007210 R115 0x007303 R116 0x007400 R117 0x007500 R118 0x007600 R119 0x007700 R120 0x007800 R121 0x007900 R122 0x007A00 R123 0x007B28 R124 0x007C00 R125 0x007D11 R126 0x007E79 R127 0x007F7A R128 0x008000 R129 0x008101 R130 0x008200 R131 0x008301 R132 0x008401 R133 0x008577 R134 0x008600 R135 0x00876E R136 0x008800 R137 0x008900 R138 0x008A00 R139 0x008B03 R140 0x008C02 R141 0x008D00 R142 0x008E01 R143 0x008F01 R144 0x009077 R145 0x009101 R146 0x009289 R147 0x009320 R149 0x00950D R150 0x009600 R151 0x009701 R152 0x00980D R153 0x009929 R154 0x009A24 R155 0x009B32 R156 0x009C01 R157 0x009D00 R158 0x009E00 R159 0x009F00 R160 0x00A0FC R161 0x00A132 R162 0x00A200 R164 0x00A400 R165 0x00A500 R167 0x00A701 R178 0x00B200 R180 0x00B400 R181 0x00B500 R182 0x00B600 R183 0x00B700 R184 0x00B800 R185 0x00B905 R186 0x00BA08 R187 0x00BB00 R188 0x00BC00 R189 0x00BD00 R190 0x00BE2C R191 0x00BF00 R192 0x00C050 R193 0x00C100 R194 0x00C200 R195 0x00C300 R196 0x00C400 R197 0x00C51D R198 0x00C600 R199 0x00C700 R200 0x00C81D R201 0x00C900 R202 0x00CA00 R203 0x00CB00 R204 0x00CC15 R205 0x00CD00 R206 0x00CE00 R207 0x00CF15 R208 0x00D000 R209 0x00D114 R210 0x00D200 R211 0x00D316 R212 0x00D400 R213 0x00D514 R214 0x00D600 R215 0x00D716 R216 0x00D80F R217 0x00D900 R218 0x00DA00 R219 0x00DB19 R220 0x00DC6E R221 0x00DD00 R222 0x00DE03 R223 0x00DF0D R224 0x00E047 R225 0x00E100 R226 0x00E200 R227 0x00E319 R228 0x00E46E R229 0x00E500 R230 0x00E603 R231 0x00E70D R232 0x00E847 R233 0x00E90A R234 0x00EA0A R235 0x00EB00 R236 0x00ECC3 R237 0x00ED50 R238 0x00EE00 R239 0x00EF00 R240 0x00F0C3 R241 0x00F150 R242 0x00F200 R243 0x00F300 R244 0x00F400 R249 0x00F912 R250 0x00FA00 R251 0x00FB13 R252 0x00FC2C R253 0x00FD00 R254 0x00FE00 R255 0x00FF00 R256 0x010000 R257 0x010101 R258 0x010200 R259 0x010301 R260 0x010402 R261 0x010580 R262 0x010600 R263 0x010700 R264 0x010800 R265 0x010900 R266 0x010AC8 R267 0x010BA0 R268 0x010C0C R269 0x010D0A R270 0x010E02 R271 0x010F14 R272 0x011000 R273 0x011100 R274 0x011200 R275 0x01130E R276 0x01140C R277 0x01150E R278 0x011609 R279 0x011708 R280 0x011809 R281 0x011907 R282 0x011A0D R283 0x011B07 R284 0x011C1E R285 0x011D1E R286 0x011E02 R287 0x011F30 R288 0x012000 R289 0x0121EE R290 0x012202 R291 0x0123CA R292 0x012409 R293 0x012501 R294 0x012600 R295 0x01272C R296 0x012808 R297 0x01290C R298 0x012A08 R299 0x012B01 R300 0x012C00 R301 0x012D1C R302 0x012E20 R303 0x012F01 R304 0x013001 R305 0x013100 R306 0x013200 R307 0x013300 R308 0x013410 R309 0x0135AA R310 0x0136AA R311 0x0137AA R312 0x0138AA R313 0x0139AA R314 0x013AFF R315 0x013BFF R316 0x013CFF R317 0x013DFF R318 0x013EFF R319 0x013F03 R320 0x014000 R321 0x01410A R322 0x014200 R323 0x014324 R324 0x01449F R325 0x014500 R326 0x014600 R327 0x014798 R328 0x014896 R329 0x014980 R330 0x014A00 R331 0x014B64 R332 0x014C00 R333 0x014D00 R334 0x014E00 R335 0x014F00 R336 0x015000 R337 0x015198 R338 0x015296 R339 0x015300 R340 0x015400 R341 0x015500 R342 0x015600 R343 0x015700 R344 0x015800 R345 0x015900 R346 0x015A02 R347 0x015B00 R348 0x015C00 R349 0x015D00 R350 0x015E00 R351 0x015F00 R352 0x016000 R357 0x016528 R367 0x016F00 R411 0x019B0C

本身APLL2的jitter性能也没有APLL1的要好。

有没有将APLL2的输出改为差分LVPECL或LVDS输出,是否也是有这样的抖动和频偏?

因为我看APLL2的输出配置的都是HSCL和CMOS单端输出,配置为差分输出比单端 的相位噪声要低。

是这样的,我注意到了APLL2的抖动性能要稍弱一些,但是我们在outputs页设置的是25M的输出,结果得到的是28M的输出(虽然可能是因为抖动的原因),这个时钟是无法使用的;我在单独使用APLL1的实验中输出同样的时钟频率,测量得到的结果就是正常的(指的是示波器上不会观测到使用APLL2的这种情况,测量结果为25M),125fs的jitter抖动在我们设置的频率上应该影响不明显(我所使用的示波器应当是无法捕捉的,所以我才会认为APLL2没有锁定成功,导致输出的时钟频率/相位在跳动)

您所给出的APLL2的输出改为LVPECL或LVDS输出的方式如果是指TICSPRO的设置,那您给出的配置文件中就是这个设置,结果是不正常的;

如果是指硬件上的修改,那我做过尝试,由于OUTPUT0的硬件外围设置的是匹配LVDS的输出形式,所以我将OUTPUT0的输出源设置为APLL2,得到的时钟频率同样是不对的;

然后我还做过其他实验,包括:单独使用APLL1,这时候所有的输出都正常;单独使用APLL2,输出不正常;

所以有没有可能是APLL2的某项设置不对,上面我有附有硬件连接图

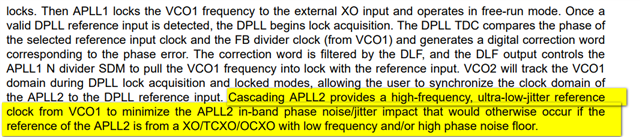

配置应该是没问题,问题应该是出在这里:就是APLL2的输入我们使用的是XO作为参考,如下图,使用级联APLL2(也就是APLL1的输出经过分频和MXU作为APLL2的输入),可以提供高频,低抖动参考时钟,减少APLL2的带内相位噪声。 如果APLL2参考来自于低频或者高相位底噪的XO,就很有可能由于APLL2的带内噪声造成输出抖动。