Part Number: CDCE6214

工程师你好!

我们使用TICS Pro 配置了CDCE6214,发现LVDS 1.8V输出的摆幅有1.8V,与手册中提及的0.3V不同,请问是哪里有配置出错吗?

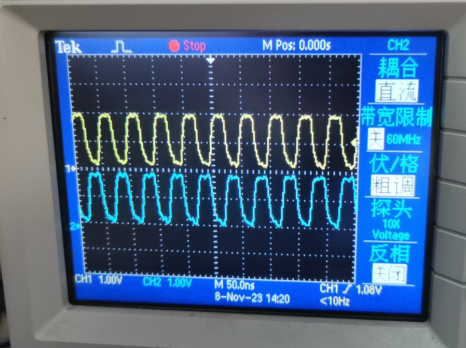

20MHz输出的PN差分波型:

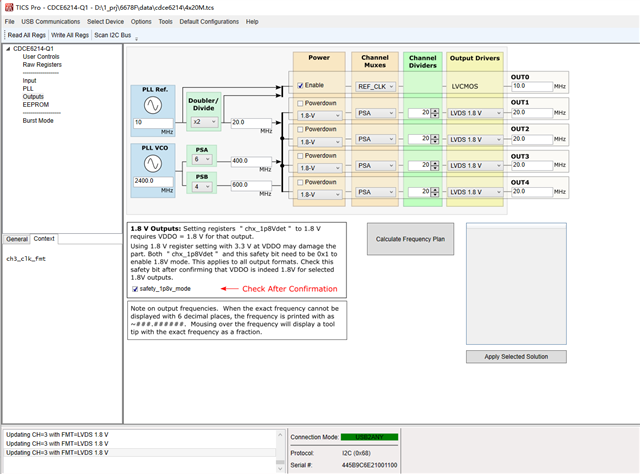

配置:

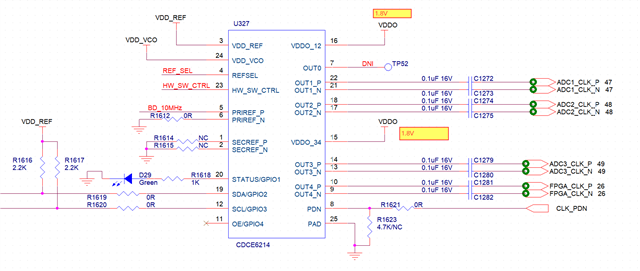

电路:

请帮忙看下,是否有问题,感谢!

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好,您测试的是在经过0.1uF电容后的波形是吗?因为我看共模电压为0

.正常LVDS输出共模为1.2V。所以要在靠近芯片输出端测试。

300mV指的是Vod=(Vout+)-(Vout-).所以1.2V共模电压,输出单端波形应该1.05V~1.35V范围。

另外,建议您使用差分碳棒直接测量差分输出,波形更为直观。

另外,补充下,您看下输出寄存器的配置,是否配置的为LVDS 输出,从波形来看,像是输出的CMOS输出。

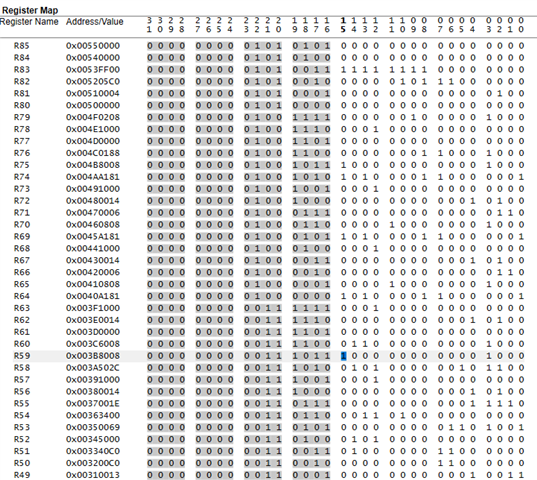

比如OUT1输出的配置寄存器R59 的bit15是否enable LVDS输出。

感谢回复,

.正常LVDS输出共模为1.2V。所以要在靠近芯片输出端测试。

有在近芯片测试,也是一样。

OUT1输出的配置寄存器R59 的bit15是否enable LVDS输出。

看起来都是有设置成LVDS的。

有个怀疑,是不是输出阻抗不匹配,请问这个芯片的输出阻抗是多少呢?

配置为LVDS输出的时候,建议在靠近接收端,或者使用差分碳棒测量的时候,在PN端接一个100ohm匹配电阻防止阻抗不匹配。

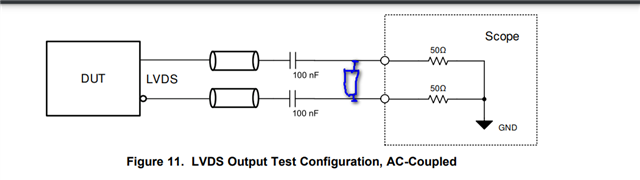

类似下图,或者每个碳棒配置50ohm阻抗,二者都可以。