Part Number: CDCE62005

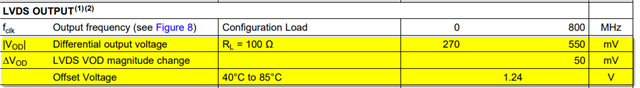

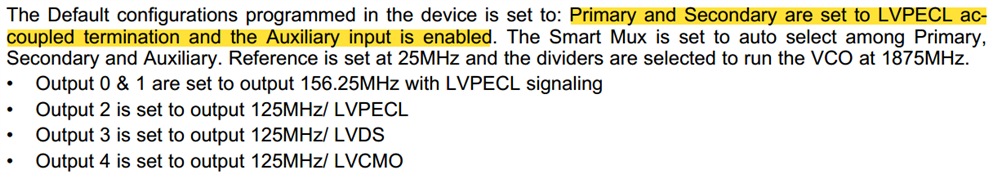

我注意到芯片的默认工作情况为下图所示:

我现在使用AUX_IN输入25MHz单端时钟(方波 2Vpp 无偏置 HiZ)

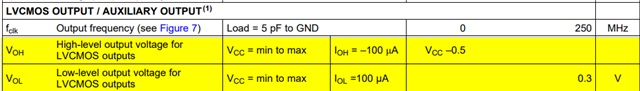

此时PLL_LOCK为持续高电平——PLL成功锁定,且U3和U4有正确频率的波形,但U0、U1、U2只有直流偏置却没有输出时钟波形,请问这可能是什么原因呢?

另外,U3和U4的输出偏置电压为1.6V,正常吗?我使用的输入时钟应不应该设置偏置?

【补充说明:】

实测整个芯片的各个VCC引脚均供电正常,VBB为1.38V也正常,外部配置引脚REF_SEL、PowerDown、SYNC均为高电平。

期待您的指点和回复!谢谢!